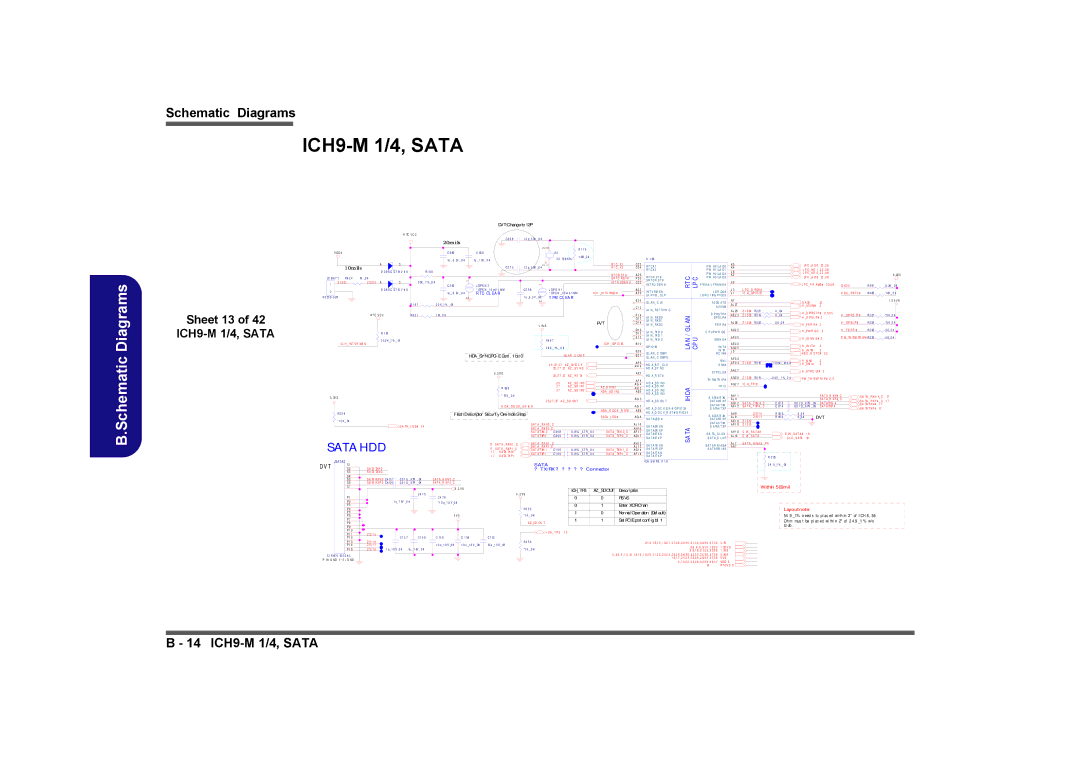

Schematic Diagrams

ICH9-M 1/4, SATA

B.Schematic Diagrams![]()

Sheet 13 of 42

ICH9-M 1/4, SATA

|

|

|

|

|

|

|

|

| DVT:Change to 12P |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

| R TC V CC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

| 20m ils |

|

| C2 6 8 | 1 2 p_ 5 0V _0 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| 3 4 |

|

|

|

| R1 7 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| V DD3 |

|

|

| C5 66 | C 55 9 |

|

|

| X 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

| 1u _ 6. 3V _ 0 4 | . 1u _ 1 6V _ 0 4 |

|

| 3 2 . 76 8 K Hz | 1 0M _0 4 |

|

|

| U 1 5A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

| A | C |

|

|

|

|

| 2 1 |

|

|

|

|

|

| RT C _ X 1 | C2 3 | RT CX 1 |

| F W | H0 /LA D0 | K 5 |

|

|

| LP C _A D0 | 22 ,3 8 |

|

|

|

|

| ||

|

| 10m ils |

|

|

|

|

| C2 7 5 | 1 2 p_ 5 0V _0 4 |

|

|

|

|

|

| RT C _ X 2 | C2 4 |

| K 4 |

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| RT CX 2 |

| F W | H1 /LA D1 |

|

|

| L P C _ A D 1 | 2 2 ,3 8 |

|

|

|

|

| |||||||||

|

|

| D 3 9 S C S 7 51 V |

| R1 6 8 |

|

|

|

|

|

|

|

|

|

| RT CR S T # | A 2 5 |

|

| F W | H2 /LA D2 | L 6 |

|

|

| L P C _ A D 2 2 2 , 3 8 |

|

|

|

| 3 . 3V S | ||||

JC B A T 1 | R4 2 4 | 1K _0 4 |

|

|

|

|

|

|

|

|

|

|

|

|

| RT CR S T # | C C | K 2 |

|

|

| LP C _A D3 | 22 ,3 8 |

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| S R T C R S T # | F 2 0 | F W | H3 /LA D3 |

|

|

|

|

|

|

|

|

| ||||||||||

| Z 1 3 01 | Z 13 0 2 A | C | 2 0K _ 1 % _0 4 | 1 |

|

|

|

|

|

|

|

|

| I N T R U D E R # | C2 2 | S RT CR S T # |

|

| K 3 |

|

|

|

|

|

|

|

|

|

|

|

| |||

1 |

|

|

| 1 |

|

|

|

|

|

| INT RU DE R # | RT LP | F W H4 /L F RA M E # |

|

|

| L P C _ F R A ME # | 2 2,3 8 |

|

|

|

|

| ||||||||||||

|

| D 3 8 S C S 7 51 V |

| C2 59 | J OP E N 2 |

| J OP E N1 |

|

|

|

|

| B 2 2 | J 3 | L P C _ D RQ0 # |

| G A 2 0 |

| R4 91 |

| 8 . 2K _ 0 4 | ||||||||||||||

2 |

|

|

| 1u _ 6. 3V _ 0 4 | * OP E N _1 0 mi l | C 2 5 8 |

|

|

| ICH _IN TV RME N | INT V RM E N |

|

| L DR Q0 # |

|

|

|

|

| K B C _ RS T C# | R4 69 |

| 1 0K _ 0 4 | ||||||||||||

|

|

|

|

| R TC | CL EA R |

| * OP E N _1 0 m il |

| A 2 2 |

|

| J 1 | IC H _ GP IO 23 |

|

|

|

|

|

| |||||||||||||||

8 5 20 5 |

|

|

|

|

| 1 u _6 . 3 V _ 04 | T PM CL EA R |

|

|

|

| LA N1 00 _ S L P |

| L DRQ 1 #/G P IO2 3 |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

| 2 |

|

|

|

|

| E 2 5 |

|

|

|

| N7 |

|

|

|

|

|

|

|

|

|

|

| 1 . 0 5 V S | |||||||

|

|

|

|

|

|

|

|

| 2 |

|

|

| GL A N _ C LK |

|

| A 2 0G A T E |

|

|

| G A 20 |

| 22 |

|

|

|

|

| ||||||||

|

|

|

|

| R1 6 7 | 2 0 K _1 % _ 04 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| A J 27 |

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| C1 3 |

|

|

| A 2 0 M# |

|

|

| H _A 2 0 M# 2 |

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| LA N _ RS T S Y N C | AN |

| A J 25 | Z 1 3 04 | R2 21 | 0 _ 04 |

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| D P RS T P # | H _D P RS T P # | 2 ,5,3 5 |

|

|

|

|

| |||||||||

|

|

| R T C V C C |

| R4 5 1 | 1 M_ 0 4 |

|

|

|

|

|

|

|

|

|

|

| F 1 4 |

| A E 2 3 Z 1 3 05 R5 19 | 0 _ 04 | H _ DP RS TP # | R2 27 |

| *5 6 _0 4 | ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| G1 3 | LA N _ RX D0 |

| DP S L P # |

|

|

|

| H _D P S L P # 2 |

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

| 1 . 5V S |

|

|

|

|

|

| PVT | D1 4 | LA N _ RX D1 | GL |

| F E R R# | A J 26 | Z 1 3 06 R2 22 | 5 6 _0 4 | H _F E R R # | 2 |

| H _ DP S L P # |

| R5 29 |

| *5 6 _0 4 | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| LA N _ RX D2 |

|

|

|

| |||||||||||||||

|

|

| R 1 81 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| D1 3 | LA N _ TX D 0 | / | C P UP W R GD | A D2 2 |

|

|

| H _P W R GD 2 |

| H _ F E RR # |

| R2 28 |

| 5 6_ 0 4 | |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| D1 2 |

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| E 1 3 | LA N _ TX D 1 | N U |

|

| A F 2 5 |

|

|

| H _I G N N E # 2 |

| P M_ TH RM TR IP # R5 28 |

| 5 6_ 0 4 | ||||

|

|

| 3 3 2 K _1 % _ 06 |

|

|

|

|

| R 4 4 7 |

|

|

|

|

|

| LA N _ TX D 2 |

| IGNN E # |

|

|

|

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| ICH _ GP IO 56 | B 1 0 |

| A E 2 2 |

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

| IC H _ INT V R ME N |

|

|

|

|

|

|

|

|

|

|

|

|

| GP IO 56 | LA CP |

| INIT # |

|

|

| H _IN IT # |

| 2 |

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

| 2 4. 9 _ 1% _ 0 4 |

|

|

|

| B 2 8 |

| A G2 5 |

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| GL A N _ C OMP I |

|

| IN TR | L 3 |

|

|

| H _I N TR |

| 2 | 2 2 |

|

|

|

|

| |

|

|

|

|

|

|

| HDA_SYNC:PCI- E Conf . 1 bit 0 |

|

|

| GL A N _C OM P |

|

| B 2 7 |

|

| RC IN# |

|

|

|

| K B C _R S T C # |

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

| GL A N _ C OMP O |

|

| NM I | A F 2 3 |

|

|

| H _N MI |

| 2 |

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

| 2 5 ,27 ,3 7 | A Z _ B ITC L K |

|

| A F 6 | HD A _B IT _ CL K |

|

| S MI# | A F 2 4 | Z 1 3 07 R 5 16 | *1 0 mi l _ sh o rt | H _S M I# |

| 2 |

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

| A H 4 |

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

| 25 ,2 7 ,37 | A Z _ S Y NC |

|

|

| HD A _S Y NC |

|

|

| A H2 7 |

|

|

| H _S T P C LK # 2 |

|

|

|

|

| ||||||

|

|

|

|

|

|

|

| 3 . 3 V S |

|

|

|

|

|

|

|

| A E 7 |

|

|

| S T P CL K # |

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

| 25 , 2 7 , 37 A Z _ R S T# |

|

| HD A _R S T # |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| A G2 6 Z 1 3 08 R 5 15 | 5 4. 9 _ 1 %_ 0 4 | P M _T H R MT R I P # 2 , 5 |

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| A F 4 |

|

| TH RM TR IP # |

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

| 2 5 |

|

| A Z _ S D IN0 |

|

| HD A _S D IN0 |

| A G2 7 | I C H _ T P 12 |

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| A G 4 | DA |

| T P 1 2 |

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

| R 53 3 |

| 2 7 |

|

| A Z _ S D IN1 |

| A Z _S D I N 2 | A H 3 | HD A _S D IN1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

| 3 7 |

|

| A Z _ S D IN2 |

| HD A _S D IN2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| H D A _ S D I N 3 | A E 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

| * 10 K _ 0 4 |

|

|

|

|

|

|

|

|

| HD A _S D IN3 | IH |

|

| A H1 1 |

|

|

|

|

| S A T A _R X N 4 _C | S A TA _ RX N 4_ C 17 | |||||

3. 3V S |

|

|

|

|

|

|

|

| 2 5,2 7 ,37 | A Z _ S D OUT |

|

|

| A G 5 | HD A _S D OU T | S A TA 4 R XN | A J 11 |

|

|

|

|

| S A T A _R X P 4_ C | ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| S A T A 4R X P | A G1 2 | S A T A _ T XN 4_ C | C 67 3 | 0. 0 1 U _ X 7R _ 04 S A T A TX N 4 |

| S A TA _ RX P 4 _ C | 1 7 | |||||||||||||

|

|

|

|

|

|

|

|

| H D A _ D O C K _ E N #_ R |

|

|

|

|

|

|

| A G 7 |

|

| S A T A 4 T XN |

| S A TA T X N 4 1 7 |

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| HD A _D OC K _E N # /GP IO 33 | A F 1 2 S A T A _ T XP 4 _ C | C 67 4 | 0. 0 1 U _ X 7R _ 04 S A T A TX P 4 |

| S A TA T X P 4 | 17 |

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| HDA _ D OCK _R S T# | A E 8 | S A TA 4 T X P |

|

|

|

|

|

|

|

|

|

| ||||||

| R2 2 4 |

|

|

| Flash Descriptor Securit y Override Strap |

|

|

|

|

|

| HD A _D OC K _R S T #/G P IO3 4 |

|

| A H9 |

| Z 13 1 0 | R 65 9 | 0 _0 4 |

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

| S A TA _L E D# | A G 8 | S A TA 5 R XN |

| DVT |

|

|

|

|

| ||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| S A T A LE D # |

| A J 9 |

| Z 13 1 1 | R 66 0 | 0 _0 4 |

|

|

|

|

| ||||||||||||

| *1 0 K _ 04 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| S A T A 5R X P | A E 1 0 Z 1 3 12 |

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

| S A T A _ RX N0 _ C |

|

|

|

|

|

| A J 1 6 |

|

| S A T A 5 T XN |

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

| S A TA _ L E D # 2 4 |

|

|

|

|

|

|

|

|

|

| S A T A 0R X N |

| A F 1 0 | Z 1 3 13 |

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

| S A T A _ RX P 0 _C |

|

|

|

|

|

| A H1 6 | TA | S A TA 5 T X P |

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| S A T A T XN 0 | C4 9 8 |

| 0 . 01 U _X 7 R _ 0 4 | S A T A _ TX N 0_ C | A F 1 7 | S A T A 0R X P | S A TA _ CL K N | A H1 8 | C LK _ S A T A # | C LK _ S A T A # 1 8 |

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

| S A T A T XP 0 | C4 9 9 |

| 0 . 01 U _X 7 R _ 0 4 | S A T A _ TX P 0 _ C | A G1 7 | S A T A 0T X N | A J 18 | C LK _ S A T A |

|

|

|

|

|

|

|

| |||||||||

SATA HDD |

|

|

|

|

|

|

| S A T A 0T X P | SA | S A T A _C L K P | CL K _ S A TA 18 |

|

|

|

|

|

|

|

| ||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

| 17 | S A T A _ RX N1 _ C | S A T A _ R X N 1 _ C |

|

|

|

|

|

| A H1 3 |

| S A T A R B IA S # | A J 7 | S A T A _ RIB A S _P N |

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

| 0 . 01 U _X 7 R _ 0 4 | S A T A _ TX P 1 _ C | S A T A 1T X P |

|

|

|

|

|

|

|

|

|

| |||||||||||||||||

|

|

|

| 1 7 | S A TA TX P 1 | S A T A T XP 1 | C1 8 9 |

| A F 1 4 |

| A H7 |

|

| R 2 25 |

|

|

|

|

|

|

|

|

| ||||||||||||

|

|

|

|

|

|

|

| 17 S A T A _ R X P 1 _C | S A T A _ RX P 1 _C |

|

| 0 . 01 U _X 7 R _ 0 4 | S A T A _ TX N 1_ C | A J 1 3 | S A T A 1R X N |

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

| S A T A T XN 1 | C1 9 6 |

| A G1 4 | S A T A 1R X P |

| S A T A RB IA S |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

| 1 7 | S A TA TX N1 |

|

|

|

|

|

|

|

|

| S A T A 1T X N |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D V T | JS A T A 2 |

|

|

|

|

|

|

| SATA |

|

|

|

|

|

|

|

| ICH 9 M RE V 1. 0 |

|

|

|

|

|

| 2 4 . 9 _1 % _ 04 |

|

|

|

|

|

|

|

|

| |

| S 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

| S 2 | S A TA TX P 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

| S 3 | S A TA TX N0 |

|

|

|

|

|

| ? TX/RX? ? ? ? ? Connector |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| S 4 |

| S A TA RX N0 C4 9 7 |

| 0. 0 1 U _ X 7R _ 04 | S A T A _R X N 0 _C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||||||

|

| S 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||

|

| S 6 |

| S A TA R X P 0 C4 | 9 6 |

|

| 0. 0 1 U _ X 7R _ 04 | S A T A _R X P 0_ C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Within 500mil |

|

| ||||||||||||||

|

| S 7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 3 . 3 V S |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| C 4 7 5 |

|

|

|

|

|

|

| 3 . 3 V S |

| ICH_ TP3 | AZ_SDOUT | Description |

|

|

|

|

| ||||||||||

|

| P 1 |

|

|

|

|

|

|

|

|

|

|

|

|

| C4 7 6 |

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||

|

|

|

|

|

| . 1 u_ 1 6V _0 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 0 | 0 | RSVS |

|

|

|

|

|

| |||||||||

|

| P 2 |

|

|

|

|

|

|

|

|

|

|

|

| *1 0 u_ 1 0 V _0 8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

P 3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| R 5 3 5 |

| 0 | 1 | Enter XORChain |

|

|

| Layout note: |

| ||||||||||||||||

|

| P 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

| P 5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| *1 K _ 0 4 |

| 1 | 0 | Normal Operation (Def ault) |

|

|

|

| ||||

|

| P 6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 5 V S |

|

|

|

|

|

|

|

|

|

| |||||||||||

|

| P 8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| A Z _S D OU T |

| 1 | 1 | Set PCIE port conf ig bit 1 |

| 54 .9 _1% | n eed s to pl ac ed wi th in | 2" of I CH 8, 56 | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Oh m mus t | be pl ac ed wi thi n 2" of | 2 4.9 _1 % w/o | |||||||

|

| P 7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| st ub . |

|

|

|

| P 9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

| P 1 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| I CH _ T P 3 | 1 5 |

|

|

|

|

|

|

|

|

|

|

| P 1 1 |

| Z 13 1 5 |

|

|

| C 1 5 7 |

|

|

|

| C 1 5 8 |

|

| C 13 5 |

|

| C 1 34 |

|

| C1 33 |

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||||

|

| P 1 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||||||

|

| P 1 3 |

| Z 13 1 | 6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| R4 5 6 |

|

|

| 2, 1 4 , 1 5, 1 6 , 1 9, 2 1 , 2 7, 2 8 , 2 9, 3 0 , 3 1, 3 2 , 3 4, 3 6 , 3 7, 3 8 | 3 . 3V |

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

| 1 0 u_ 1 0 V _0 8 |

|

| 1 0 u _1 0 V _ 08 |

|

|

|

|

|

|

|

|

| |||||||||||||||||

|

| P 1 4 |

| Z 13 1 7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 10 u _1 0 V _ 08 |

|

|

| 2,3 ,4 ,5 ,9,1 6 ,1 8,3 3 | 1 . 05 V S |

|

|

|

| ||||||||||||

|

| P 1 5 |

| Z 13 1 | 8 | . 1 u_ 1 6 | V _0 4 . 1u _ | 1 6V _ 0 4 |

|

|

|

|

|

|

|

|

|

|

|

|

| *1 K _ 0 4 |

|

|

| 3 , 9, 1 6 , 2 1, 2 3 , 3 3, 3 6 | 1 . 5V S |

|

|

|

| ||||||||||

|

| 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 2 , 3, 5 , 9 , 1 2, 14 , 1 5, 1 6 , 1 9, 2 0 , 2 1, 2 2 , 2 3, 2 4 , 2 5, 2 6 , 2 8, 3 0 , 3 2, 3 3 , 3 5, 3 6 , 3 7, 3 8 | 3 . 3V S |

|

|

|

| ||

C1 6 65 6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

P IN G ND 1 ~ 2 = G ND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1 6, 1 7 , 2 1, 2 3 , 2 5, 2 6 , 2 8, 3 3 , 3 7, 3 8 | 5 V S |

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 2 ,1 9,2 2 ,2 4,2 9 ,3 2,3 3 ,3 4,3 7 | V DD 3 |

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 16 | RT CV C C |

|

|

|

| |

B - 14