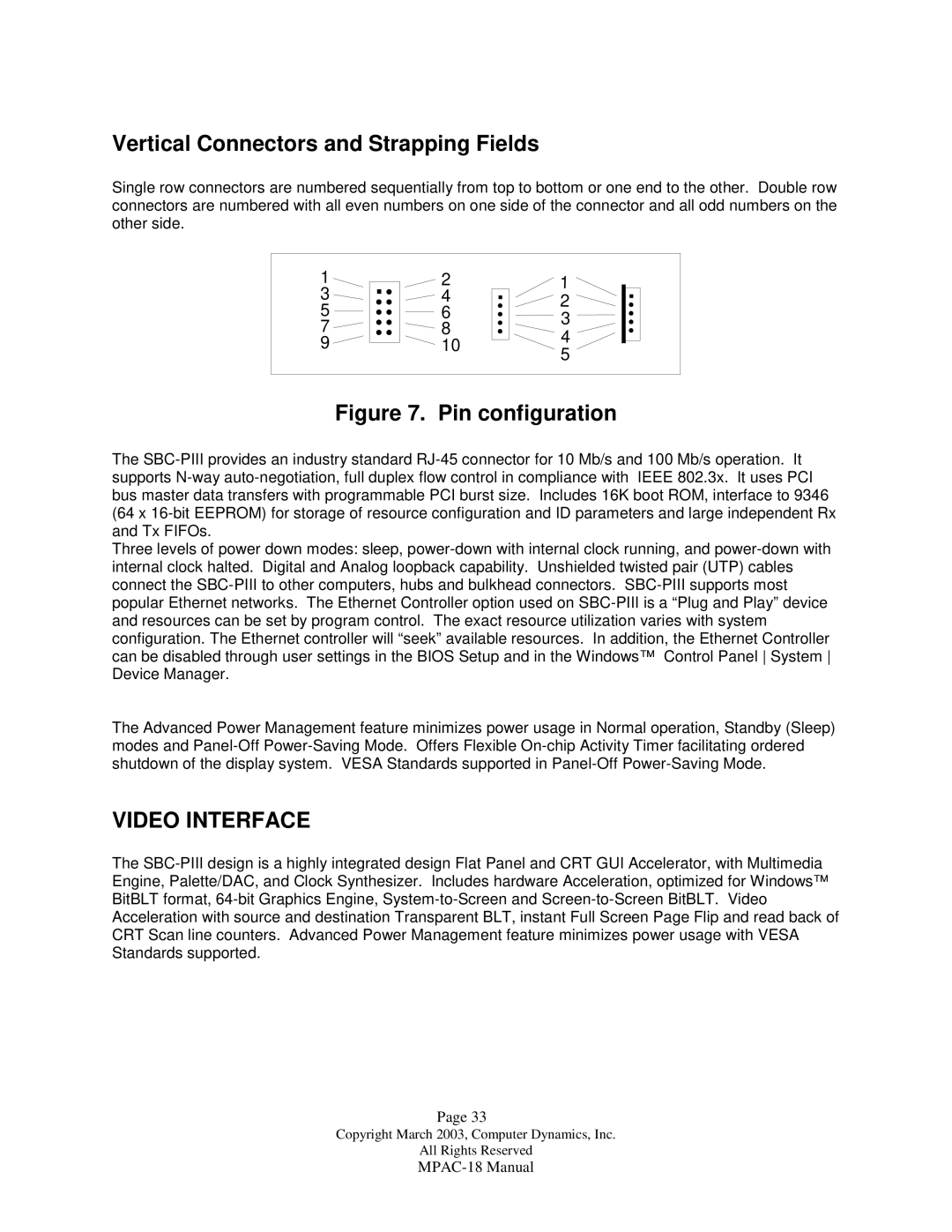

Vertical Connectors and Strapping Fields

Single row connectors are numbered sequentially from top to bottom or one end to the other. Double row connectors are numbered with all even numbers on one side of the connector and all odd numbers on the other side.

Figure 7. Pin configuration

The SBC-PIII provides an industry standard RJ-45 connector for 10 Mb/s and 100 Mb/s operation. It supports N-way auto-negotiation, full duplex flow control in compliance with IEEE 802.3x. It uses PCI bus master data transfers with programmable PCI burst size. Includes 16K boot ROM, interface to 9346 (64 x 16-bit EEPROM) for storage of resource configuration and ID parameters and large independent Rx and Tx FIFOs.

Three levels of power down modes: sleep, power-down with internal clock running, and power-down with internal clock halted. Digital and Analog loopback capability. Unshielded twisted pair (UTP) cables connect the SBC-PIII to other computers, hubs and bulkhead connectors. SBC-PIII supports most popular Ethernet networks. The Ethernet Controller option used on SBC-PIII is a “Plug and Play” device and resources can be set by program control. The exact resource utilization varies with system configuration. The Ethernet controller will “seek” available resources. In addition, the Ethernet Controller can be disabled through user settings in the BIOS Setup and in the Windows™ Control Panel System Device Manager.

The Advanced Power Management feature minimizes power usage in Normal operation, Standby (Sleep) modes and Panel-Off Power-Saving Mode. Offers Flexible On-chip Activity Timer facilitating ordered shutdown of the display system. VESA Standards supported in Panel-Off Power-Saving Mode.

VIDEO INTERFACE

The SBC-PIII design is a highly integrated design Flat Panel and CRT GUI Accelerator, with Multimedia Engine, Palette/DAC, and Clock Synthesizer. Includes hardware Acceleration, optimized for Windows™ BitBLT format, 64-bit Graphics Engine, System-to-Screen and Screen-to-Screen BitBLT. Video Acceleration with source and destination Transparent BLT, instant Full Screen Page Flip and read back of CRT Scan line counters. Advanced Power Management feature minimizes power usage with VESA Standards supported.

Page 33

Copyright March 2003, Computer Dynamics, Inc.

All Rights Reserved

MPAC-18 Manual