Connect Tech Inc. FreeForm/Express S6 - PCIe

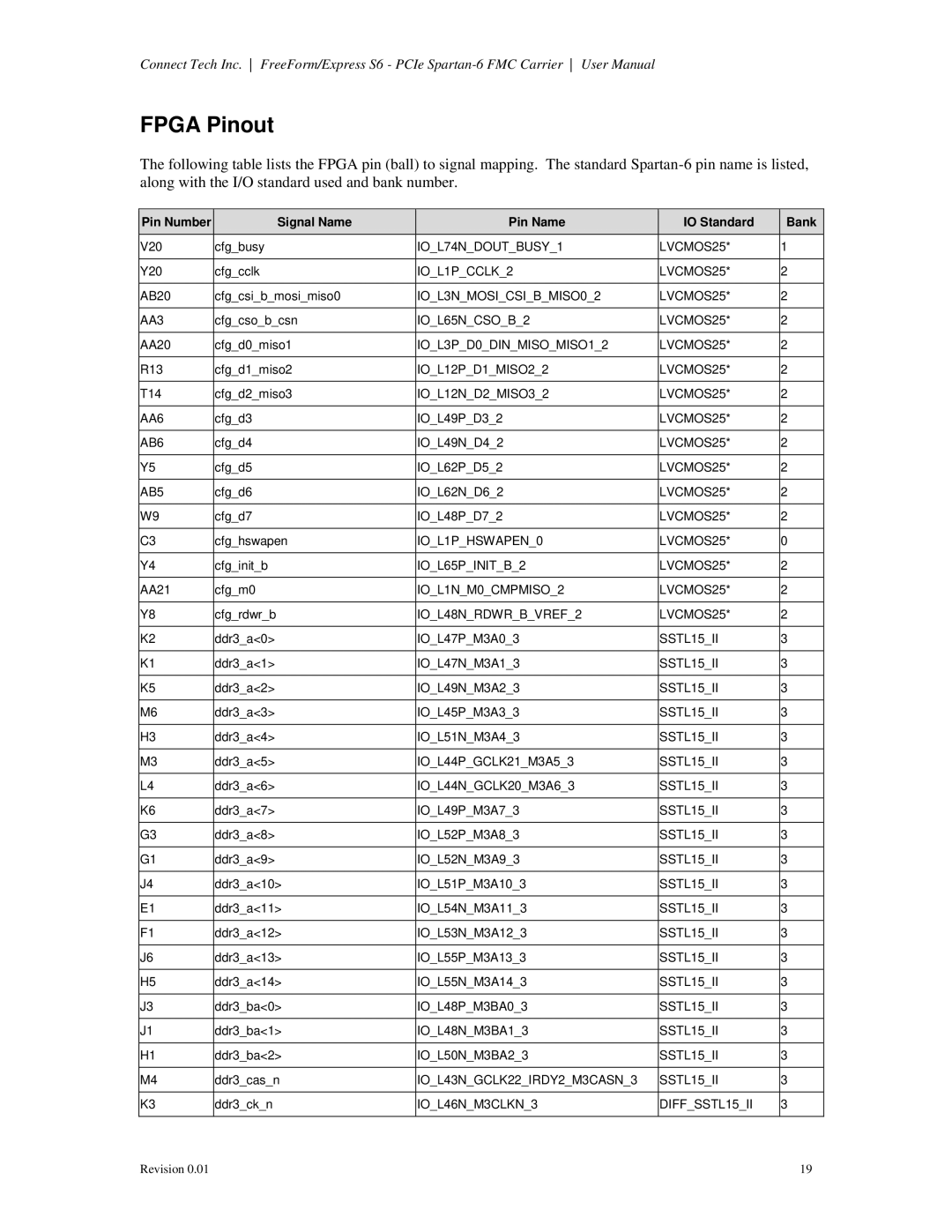

FPGA Pinout

The following table lists the FPGA pin (ball) to signal mapping. The standard

Pin Number | Signal Name | Pin Name | IO Standard | Bank | |

|

|

|

|

| |

V20 | cfg_busy | IO_L74N_DOUT_BUSY_1 | LVCMOS25* | 1 | |

|

|

|

|

| |

Y20 | cfg_cclk | IO_L1P_CCLK_2 | LVCMOS25* | 2 | |

|

|

|

|

| |

AB20 | cfg_csi_b_mosi_miso0 | IO_L3N_MOSI_CSI_B_MISO0_2 | LVCMOS25* | 2 | |

|

|

|

|

| |

AA3 | cfg_cso_b_csn | IO_L65N_CSO_B_2 | LVCMOS25* | 2 | |

|

|

|

|

| |

AA20 | cfg_d0_miso1 | IO_L3P_D0_DIN_MISO_MISO1_2 | LVCMOS25* | 2 | |

|

|

|

|

| |

R13 | cfg_d1_miso2 | IO_L12P_D1_MISO2_2 | LVCMOS25* | 2 | |

|

|

|

|

| |

T14 | cfg_d2_miso3 | IO_L12N_D2_MISO3_2 | LVCMOS25* | 2 | |

|

|

|

|

| |

AA6 | cfg_d3 | IO_L49P_D3_2 | LVCMOS25* | 2 | |

|

|

|

|

| |

AB6 | cfg_d4 | IO_L49N_D4_2 | LVCMOS25* | 2 | |

|

|

|

|

| |

Y5 | cfg_d5 | IO_L62P_D5_2 | LVCMOS25* | 2 | |

|

|

|

|

| |

AB5 | cfg_d6 | IO_L62N_D6_2 | LVCMOS25* | 2 | |

|

|

|

|

| |

W9 | cfg_d7 | IO_L48P_D7_2 | LVCMOS25* | 2 | |

|

|

|

|

| |

C3 | cfg_hswapen | IO_L1P_HSWAPEN_0 | LVCMOS25* | 0 | |

|

|

|

|

| |

Y4 | cfg_init_b | IO_L65P_INIT_B_2 | LVCMOS25* | 2 | |

|

|

|

|

| |

AA21 | cfg_m0 | IO_L1N_M0_CMPMISO_2 | LVCMOS25* | 2 | |

|

|

|

|

| |

Y8 | cfg_rdwr_b | IO_L48N_RDWR_B_VREF_2 | LVCMOS25* | 2 | |

|

|

|

|

| |

K2 | ddr3_a<0> | IO_L47P_M3A0_3 | SSTL15_II | 3 | |

|

|

|

|

| |

K1 | ddr3_a<1> | IO_L47N_M3A1_3 | SSTL15_II | 3 | |

|

|

|

|

| |

K5 | ddr3_a<2> | IO_L49N_M3A2_3 | SSTL15_II | 3 | |

|

|

|

|

| |

M6 | ddr3_a<3> | IO_L45P_M3A3_3 | SSTL15_II | 3 | |

|

|

|

|

| |

H3 | ddr3_a<4> | IO_L51N_M3A4_3 | SSTL15_II | 3 | |

|

|

|

|

| |

M3 | ddr3_a<5> | IO_L44P_GCLK21_M3A5_3 | SSTL15_II | 3 | |

|

|

|

|

| |

L4 | ddr3_a<6> | IO_L44N_GCLK20_M3A6_3 | SSTL15_II | 3 | |

|

|

|

|

| |

K6 | ddr3_a<7> | IO_L49P_M3A7_3 | SSTL15_II | 3 | |

|

|

|

|

| |

G3 | ddr3_a<8> | IO_L52P_M3A8_3 | SSTL15_II | 3 | |

|

|

|

|

| |

G1 | ddr3_a<9> | IO_L52N_M3A9_3 | SSTL15_II | 3 | |

|

|

|

|

| |

J4 | ddr3_a<10> | IO_L51P_M3A10_3 | SSTL15_II | 3 | |

|

|

|

|

| |

E1 | ddr3_a<11> | IO_L54N_M3A11_3 | SSTL15_II | 3 | |

|

|

|

|

| |

F1 | ddr3_a<12> | IO_L53N_M3A12_3 | SSTL15_II | 3 | |

|

|

|

|

| |

J6 | ddr3_a<13> | IO_L55P_M3A13_3 | SSTL15_II | 3 | |

|

|

|

|

| |

H5 | ddr3_a<14> | IO_L55N_M3A14_3 | SSTL15_II | 3 | |

|

|

|

|

| |

J3 | ddr3_ba<0> | IO_L48P_M3BA0_3 | SSTL15_II | 3 | |

|

|

|

|

| |

J1 | ddr3_ba<1> | IO_L48N_M3BA1_3 | SSTL15_II | 3 | |

|

|

|

|

| |

H1 | ddr3_ba<2> | IO_L50N_M3BA2_3 | SSTL15_II | 3 | |

|

|

|

|

| |

M4 | ddr3_cas_n | IO_L43N_GCLK22_IRDY2_M3CASN_3 | SSTL15_II | 3 | |

|

|

|

|

| |

K3 | ddr3_ck_n | IO_L46N_M3CLKN_3 | DIFF_SSTL15_II | 3 | |

|

|

|

|

|

Revision 0.01 | 19 |