CY7C09089V, CY7C09189V, CY7C09179V, CY7C09079V, CY7C09199V specifications

Cypress Semiconductor has developed a series of high-performance static random-access memory (SRAM) chips, including the CY7C09099V, CY7C09199V, CY7C09079V, CY7C09179V, and CY7C09189V. These SRAM products are designed for a wide array of applications, ranging from telecommunications and networking to consumer electronics, due to their high speed, low latency, and reliable performance.One of the most notable features of these CY7C series devices is their high-density configuration. These chips generally offer densities ranging from 256Kb to 16Mb, making them suitable for various applications requiring significant memory capacity without sacrificing speed. Additionally, they typically incorporate a low-power architecture, allowing for efficient energy consumption, which is crucial in battery-operated devices.

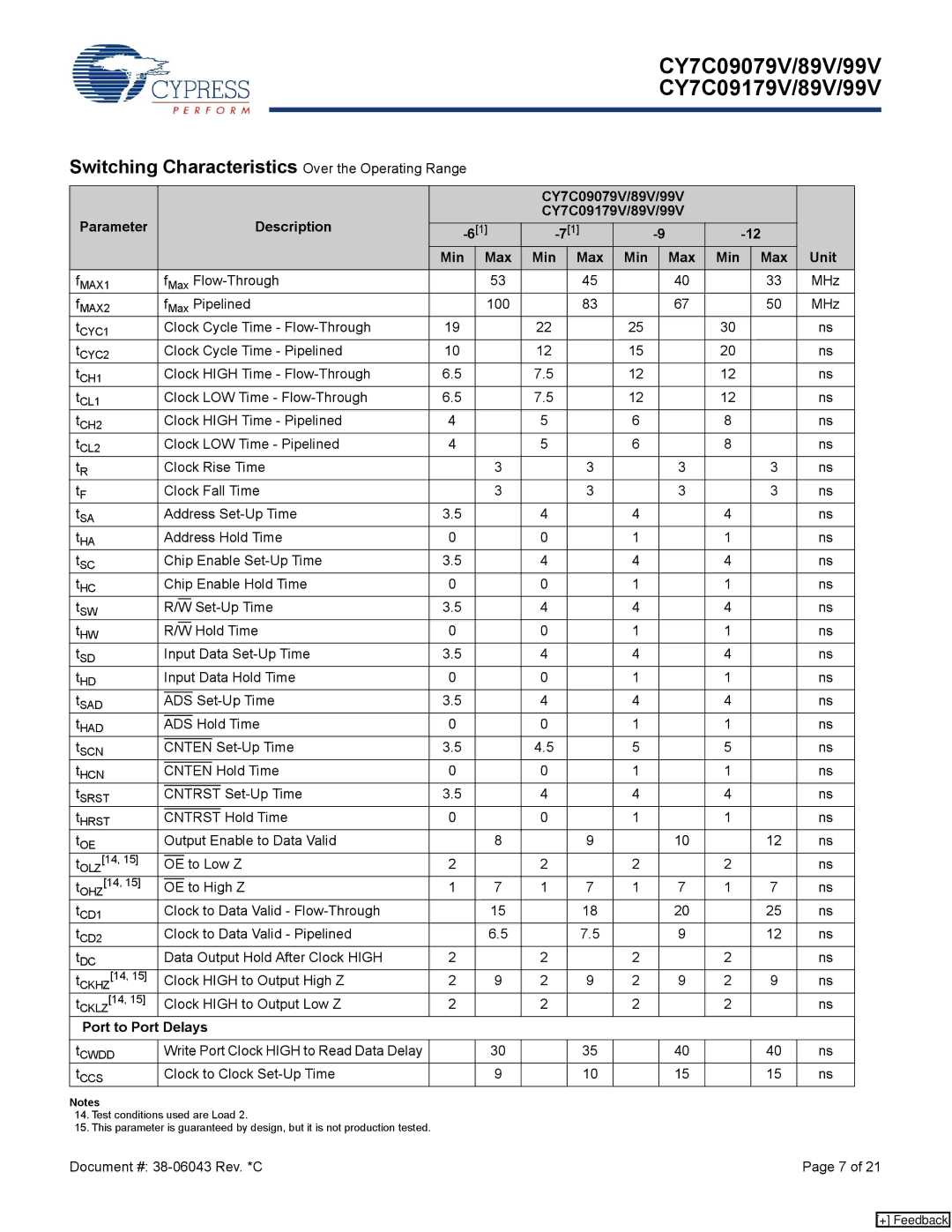

The CY7C09099V and CY7C09199V variants are particularly noted for their high-speed access times, achieving data rate performance levels that meet the stringent requirements of modern computing tasks. The read and write access times can vary from 10ns to 15ns, ensuring that these devices can handle fast data processing demands. Their robust performance is complemented by features such as a single supply voltage that simplifies circuit design while providing ease of integration into various systems.

One of the advanced technologies used in these SRAM devices is the asynchronous read and write operation. This technology allows the memory to provide quick data retrieval and storage without the need for complex timing sequences, enhancing overall system responsiveness. Moreover, the chips feature a common data input/output interface, which simplifies communication protocols and reduces design complexity.

Another essential characteristic of the CY7C series is their wide operating temperature range, making them suitable for industrial applications. The ability to operate in diverse environmental conditions increases their reliability across different sectors. Embedded parity checking within the memory architecture helps to detect and correct errors, further ensuring data integrity.

Overall, Cypress’s CY7C09099V, CY7C09199V, CY7C09079V, CY7C09179V, and CY7C09189V SRAM devices represent a significant advancement in memory technology. With a blend of high-speed performance, low power consumption, and robust reliability, they are designed to meet the evolving needs of modern electronic applications, providing designers with a reliable solution for high-performance memory requirements.