CY7C1034DV33

6-Mbit (256K X 24) Static RAM

Features

■High speed

❐tAA = 10 ns

■Low active power

❐ICC = 175 mA at 10 ns

■Low CMOS standby power

❐ISB2 = 25 mA

■Operating voltages of 3.3 ± 0.3V

■2.0V data retention

■Automatic power down when deselected

■TTL compatible inputs and outputs

■Easy memory expansion with CE1, CE2, and CE3 features

■Available in

Functional Description

The CY7C1034DV33 is a high performance CMOS static RAM organized as 256K words by 24 bits. This device has an automatic power down feature that significantly reduces power consumption when deselected.

To write to the device, enable the chip (CE1 LOW, CE2 HIGH, and CE3 LOW) while forcing the Write Enable (WE) input LOW.

To read from the device, enable the chip by taking CE1 LOW, CE2 HIGH, and CE3 LOW, while forcing the Output Enable (OE) LOW and the Write Enable (WE) HIGH. See the Truth Table on page 7 for a complete description of Read and Write modes.

The 24 IO pins (IO0 to IO23) are placed in a high impedance state when the device is deselected (CE1 HIGH, CE2 LOW, or CE3 HIGH) or when the output enable (OE) is HIGH during a write operation. (CE1 LOW, CE2 HIGH, CE3 LOW, and WE LOW).

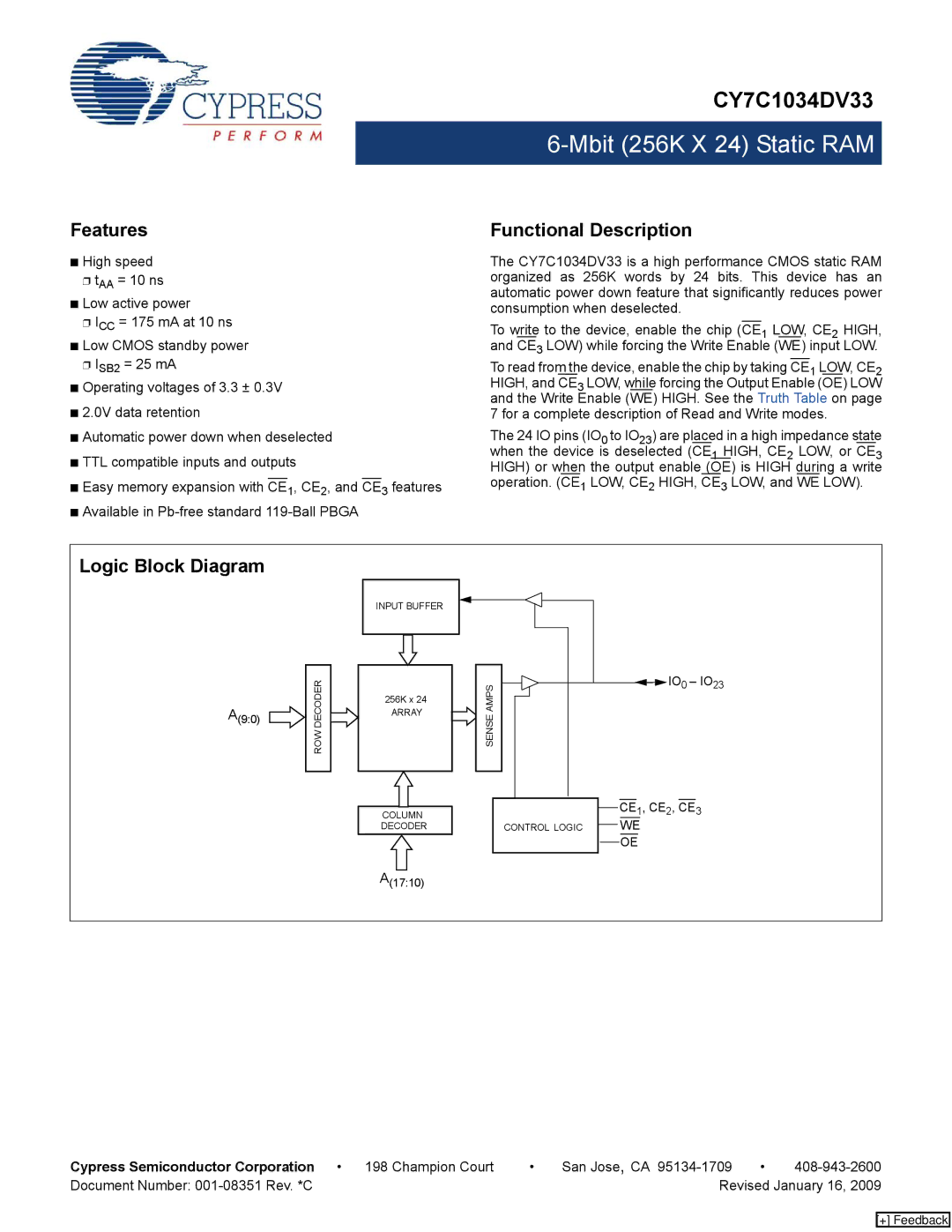

Logic Block Diagram

A(9:0) |

|

|

| DECODER |

|

|

|

|

|

|

| ||

|

|

|

|

| ||

|

|

|

| ROW |

|

|

|

|

|

|

|

|

|

INPUT BUFFER

256K x 24

ARRAY

COLUMN

DECODER

A(17:10)

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| IO0 – IO23 | ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

| SENSE AMPS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1, CE2, |

| 3 | ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| CE | CE | |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

| CONTROL LOGIC |

|

|

| WE |

| ||||||||||||

|

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| OE | |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

Cypress Semiconductor Corporation • 198 Champion Court | • | San Jose, CA | • | |

Document Number: |

| Revised January 16, 2009 | ||

[+] Feedback