|

|

|

|

| CY7C1034DV33 |

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

AC Switching Characteristics (continued) |

|

|

|

| ||||

Over the operating range [5] |

|

|

|

|

|

|

| |

Parameter |

|

| Description |

| Unit |

| ||

|

|

|

|

|

| |||

|

| Min |

| Max |

| |||

|

|

|

|

|

|

| ||

Write Cycle [9, 10] |

|

|

|

|

|

|

|

|

tWC

tSCE

tAW

tHA

tSA

tPWE

tSD

tHD

tLZWE

tHZWE

Write Cycle Time | 10 |

| ns | ||

|

| Active LOW to Write End [3] | 7 |

| ns |

CE | |||||

Address Setup to Write End | 7 |

| ns | ||

Address Hold from Write End | 0 |

| ns | ||

Address Setup to Write Start | 0 |

| ns | ||

| Pulse Width | 7 |

| ns | |

WE | |||||

Data Setup to Write End | 5.5 |

| ns | ||

Data Hold from Write End | 0 |

| ns | ||

| HIGH to Low Z [7] | 3 |

| ns | |

WE | |||||

| LOW to High Z [7] |

| 5 | ns | |

WE | |||||

Data Retention Characteristics

Over the operating range |

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

Parameter | Description |

|

|

| Conditions [3] | Min | Typ | Max | Unit | ||

VDR | VCC for Data Retention |

|

|

|

|

|

| 2 |

|

| V |

ICCDR | Data Retention Current9 | VCC | = 2V, | CE | 1, | CE | 3 > VCC – 0.2V, |

|

| 25 | mA |

|

| CE2 | < 0.2V, VIN > VCC – 0.2V or VIN < 0.2V |

|

|

|

| ||||

tCDR [11] | Chip Deselect to Data Retention Time |

|

|

|

|

|

| 0 |

|

| ns |

tR [12] | Operation Recovery Time |

|

|

|

|

|

| tRC |

|

| ns |

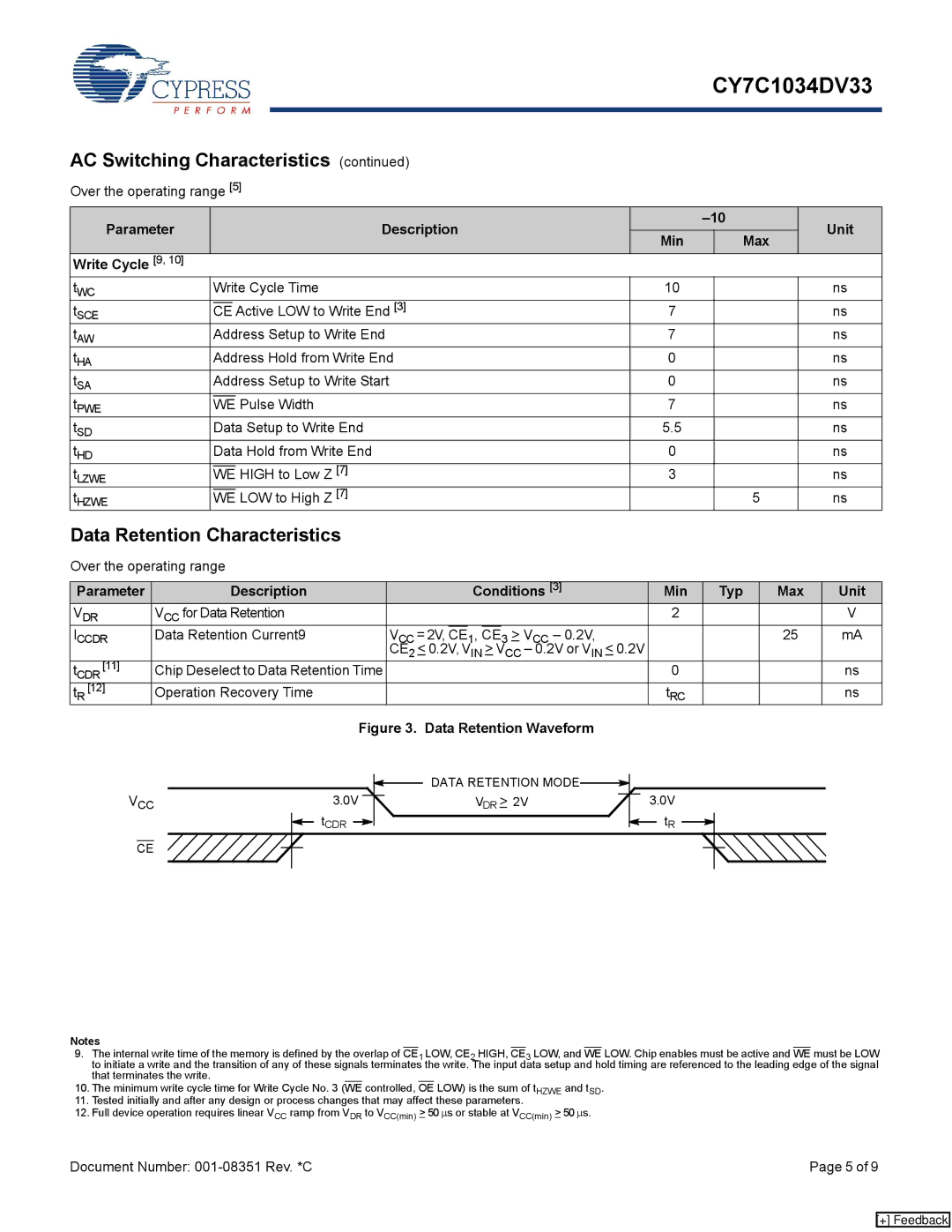

Figure 3. Data Retention Waveform

|

| DATA RETENTION MODE |

|

VCC | 3.0V | VDR > 2V | 3.0V |

| tCDR |

| tR |

CE |

|

|

|

Notes

9.The internal write time of the memory is defined by the overlap of CE1 LOW, CE2 HIGH, CE3 LOW, and WE LOW. Chip enables must be active and WE must be LOW to initiate a write and the transition of any of these signals terminates the write. The input data setup and hold timing are referenced to the leading edge of the signal that terminates the write.

10.The minimum write cycle time for Write Cycle No. 3 (WE controlled, OE LOW) is the sum of tHZWE and tSD.

11.Tested initially and after any design or process changes that may affect these parameters.

12.Full device operation requires linear VCC ramp from VDR to VCC(min) > 50 μs or stable at VCC(min) > 50 μs.

Document Number: | Page 5 of 9 |

[+] Feedback