CY7C1034DV33

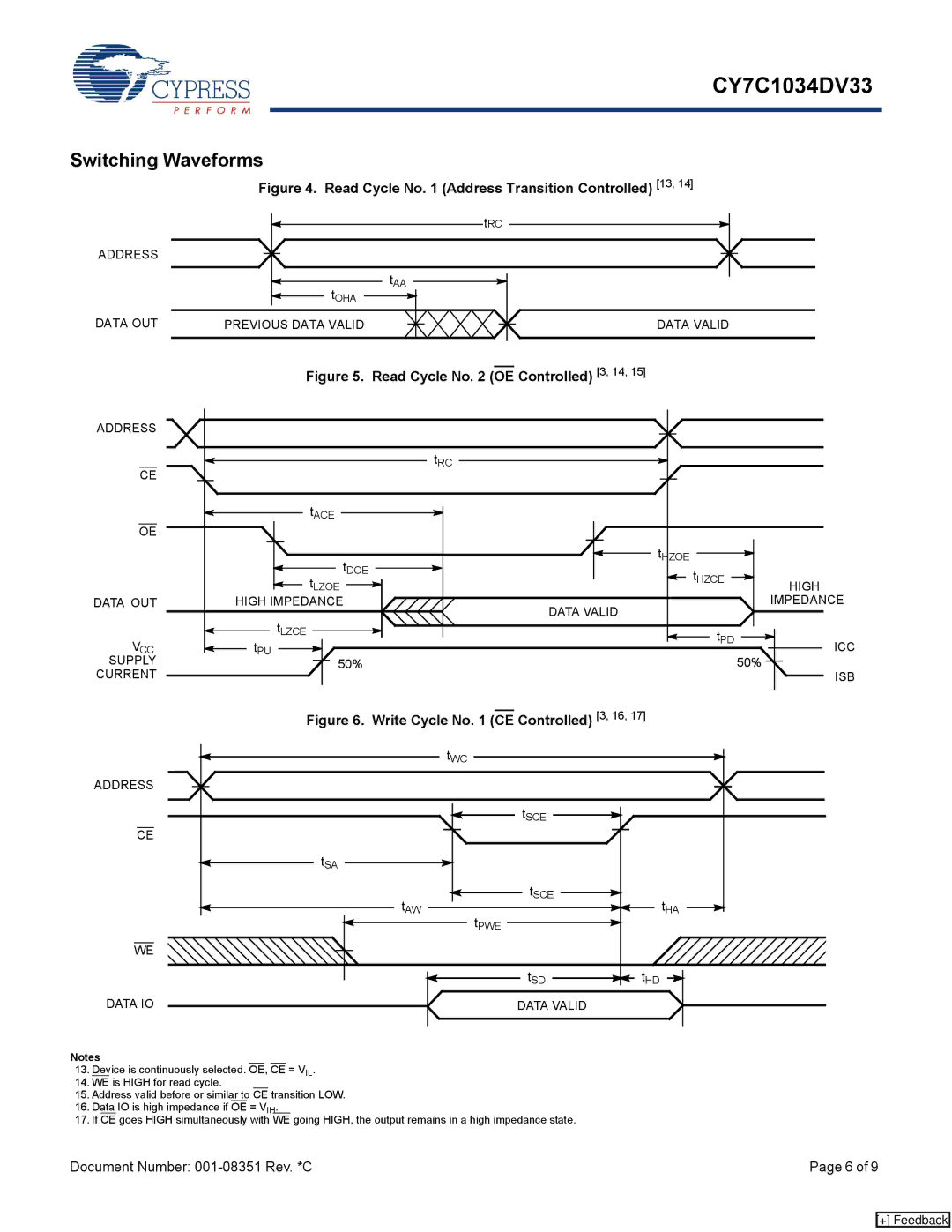

Switching Waveforms

Figure 4. Read Cycle No. 1 (Address Transition Controlled) [13, 14]

tRC

ADDRESS

tAA

tOHA

DATA OUT | PREVIOUS DATA VALID |

|

|

|

| DATA VALID |

|

| |||||

|

|

|

|

|

|

|

| Figure 5. Read Cycle No. 2 (OE Controlled) [3, 14, 15] |

| ||

ADDRESS |

|

|

|

|

CE |

| tRC |

|

|

|

|

|

| |

| tACE |

|

|

|

OE |

|

|

|

|

| tDOE |

| tHZOE |

|

|

| tHZCE |

| |

| tLZOE |

| HIGH | |

DATA OUT | HIGH IMPEDANCE | DATA VALID |

| IMPEDANCE |

|

|

|

| |

| tLZCE |

| tPD |

|

VCC | tPU |

| ICC | |

SUPPLY | 50% |

|

| 50% |

CURRENT |

|

|

| ISB |

| Figure 6. Write Cycle No. 1 (CE Controlled) [3, 16, 17] |

| ||

|

| tWC |

|

|

ADDRESS |

|

|

|

|

|

| tSCE |

|

|

CE |

|

|

|

|

| tSA |

|

|

|

| tAW | tSCE | tHA |

|

| tPWE |

| ||

|

|

|

| |

WE |

|

|

|

|

|

| tSD | tHD |

|

DATA IO |

| DATA VALID |

|

|

Notes

13.Device is continuously selected. OE, CE = VIL.

14.WE is HIGH for read cycle.

15.Address valid before or similar to CE transition LOW.

16.Data IO is high impedance if OE = VIH.

17.If CE goes HIGH simultaneously with WE going HIGH, the output remains in a high impedance state.

Document Number: | Page 6 of 9 |

[+] Feedback