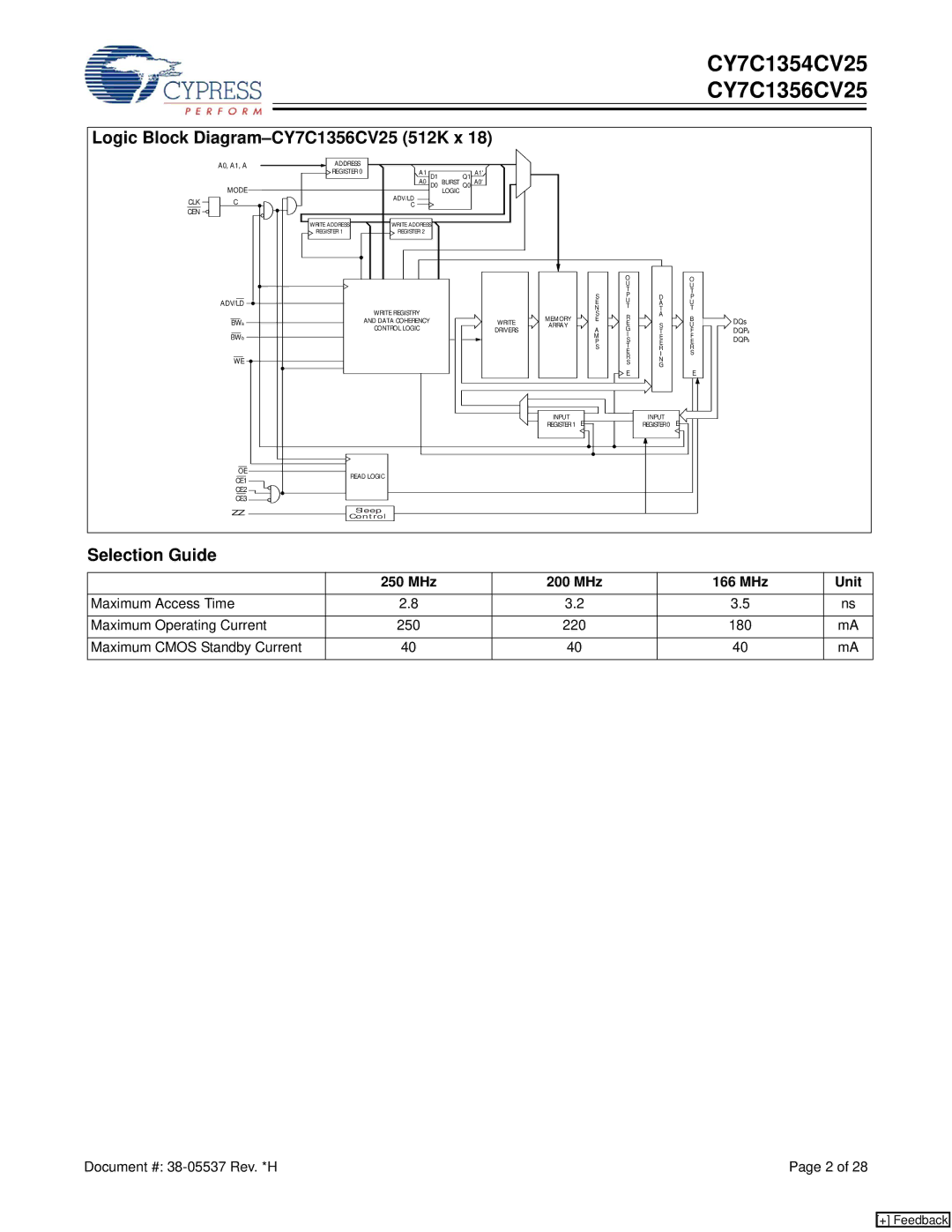

CY7C1356CV25, CY7C1354CV25 specifications

The Cypress CY7C1354CV25 and CY7C1356CV25 are high-performance, synchronous SRAM (Static Random Access Memory) devices designed for bandwidth-intensive applications. Both components are part of the Cypress family of low-power high-speed SRAMs, making them ideal for use in networking, telecommunications, and high-speed data processing systems.One of the main features of the CY7C1354CV25 and CY7C1356CV25 is their wide data bus. The CY7C1354CV25 provides a 4 Megabit memory capacity with a 36-bit wide data interface, while the CY7C1356CV25 boosts this to 6 Megabits with a similarly wide data interface. This allows for high data throughput and efficiency in applications where quick access to large data sets is critical.

Both devices offer asynchronous write and synchronous read capabilities, enabling them to support pipelines and burst accesses effectively. The memory can be accessed in a single cycle, which considerably enhances performance in applications that require quick response times, such as high-speed packet processing in routers and switches.

The Cypress SRAMs are built using advanced CMOS technology, enabling low power consumption, which is essential for mobile and battery-operated devices. Their operating voltage range, typically between 2.7V and 3.6V, contributes to the low power profile while providing a high level of performance.

Moreover, both devices support a wide temperature range, making them suitable for industrial applications. They can operate in environments from -40°C to +125°C, ensuring reliability and performance under varying conditions. This makes the CY7C1354CV25 and CY7C1356CV25 particularly valuable for automotive and aerospace applications where temperature extremes can be encountered.

Cypress has enhanced the reliability of these SRAMs with features such as built-in error detection and correction capabilities. This ensures data integrity, which is crucial for mission-critical applications.

In summary, the Cypress CY7C1354CV25 and CY7C1356CV25 ensure tight integration of high capacity, speed, and reliability. With their advanced synchronous architecture, low power consumption, and broad temperature range, they represent an excellent choice for applications that demand high performance in challenging environments. These SRAM devices continue to meet the needs of modern electronic designs, making them a trusted solution in the industry.