CY7C1399B specifications

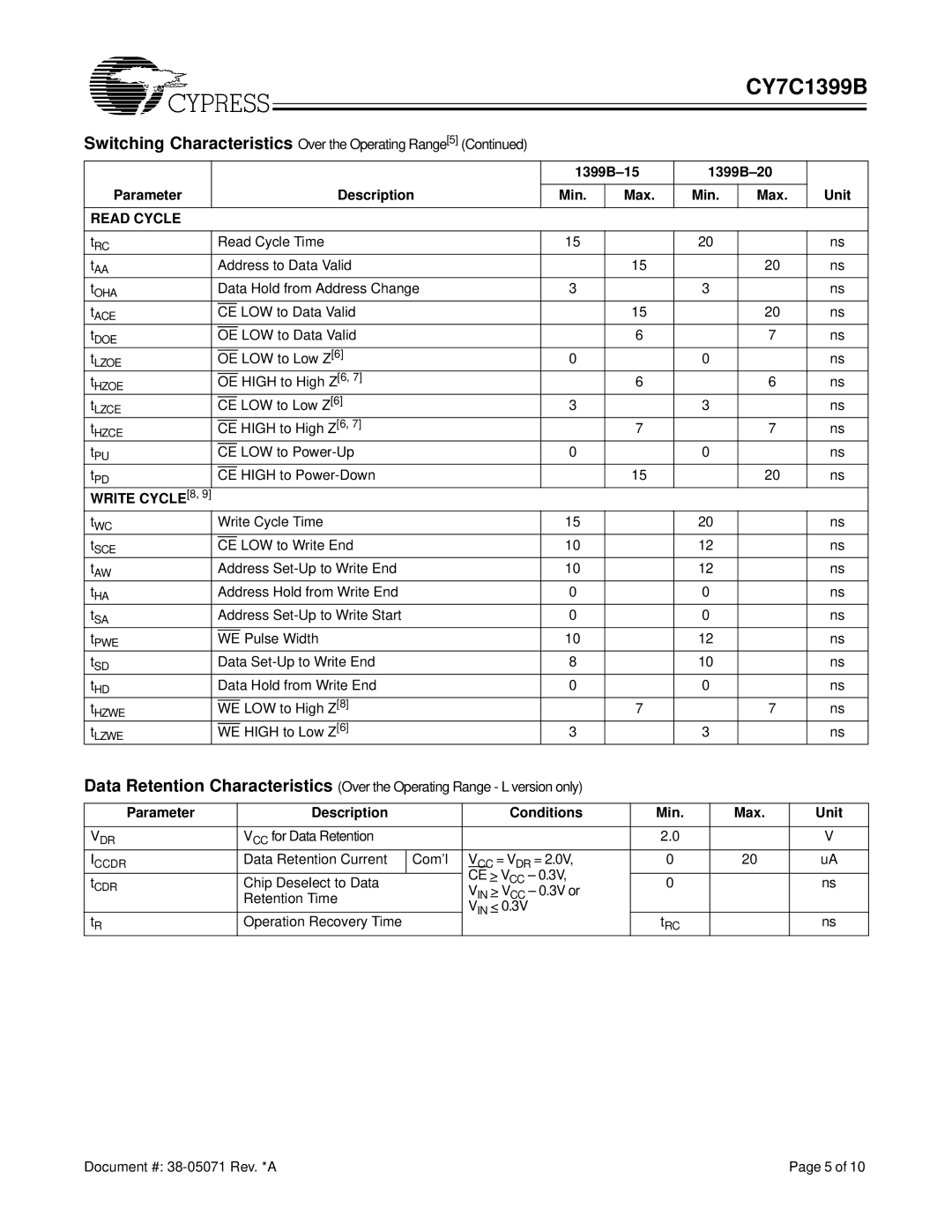

The Cypress CY7C1399B is a high-performance static random-access memory (SRAM) device that belongs to the family of asynchronous CMOS SRAMs. It is designed to deliver superior speed and efficiency, making it ideal for a multitude of applications in various fields, including telecommunications, automotive, and consumer electronics.One of the key features of the CY7C1399B is its high-speed operation, capable of achieving access times as low as 12 nanoseconds. This allows for rapid data retrieval, which is crucial in applications requiring fast data processing and real-time performance. Moreover, it operates with a single supply voltage of 2.0V to 3.6V, providing flexibility for power-sensitive designs.

The chip comes with a capacity of 16 megabits, which enables it to store substantial amounts of data. Furthermore, it features a burst mode operation that allows for efficient access to multiple consecutive data locations. This capability makes it particularly useful in applications such as video processing, where quick data retrieval is essential.

Another prominent characteristic of the CY7C1399B is its low power consumption. The device boasts both active and standby power modes, which help minimize energy usage, making it suitable for battery-operated devices. This is increasingly becoming a vital factor for consumer electronics, where energy efficiency is a priority.

In terms of interface, the CY7C1399B uses a conventional parallel interface, compatible with a variety of microcontrollers and processors. The device also supports an asynchronous read and write operation, which simplifies integration into existing systems.

The chip is built using advanced 0.18-micron CMOS technology, which not only enhances its performance but also contributes to its reliability and durability. This technology allows the CY7C1399B to achieve high integration density, resulting in a smaller footprint on printed circuit boards (PCBs).

With a combination of high-speed operational characteristics, low power consumption, and substantial data capacity, the Cypress CY7C1399B stands out as an excellent choice for designers seeking efficient memory solutions that can support the demands of modern electronic systems.