DATA BRIEF | CY7C68003 |

MoBL-USB™ TX2UL USB 2.0

ULPI Transceiver

Features

The Cypress

The TX2UL is specifically designed for mobile handset applications by offering tiny package options and low power consumption.

■USB 2.0 Full Speed and High Speed Compliant Transceiver

■

■Fully Compliant ULPI Link Interface

■

■UTMI+ Level 0 Support

■Integrated Oscillator

■Integrated PLL (13, 19.2, 24, or 26 MHz Reference)

■Integrated USB Pull Up and Termination Resistors

■3.0V to 5.775V VBATT Input

■Chip Select Pin

■Single Ended Device RESET Input

■UART Pass Through Mode

■ESD Compliance:

❐

❐

❐

■Support for Industrial Temperature Range

■Low Power Consumption for Mobile Applications:

❐5 uA Nominal Sleep Mode

❐30 mA Nominal Active HS Transfer

■Small Package for Mobile Applications:

❐2.14 x 1.76 mm

❐4 x 4 mm

Applications

■Mobile Phones

■PDAs

■Portable Media Players (PMPs)

■DTV Applications

■Portable GPS Units

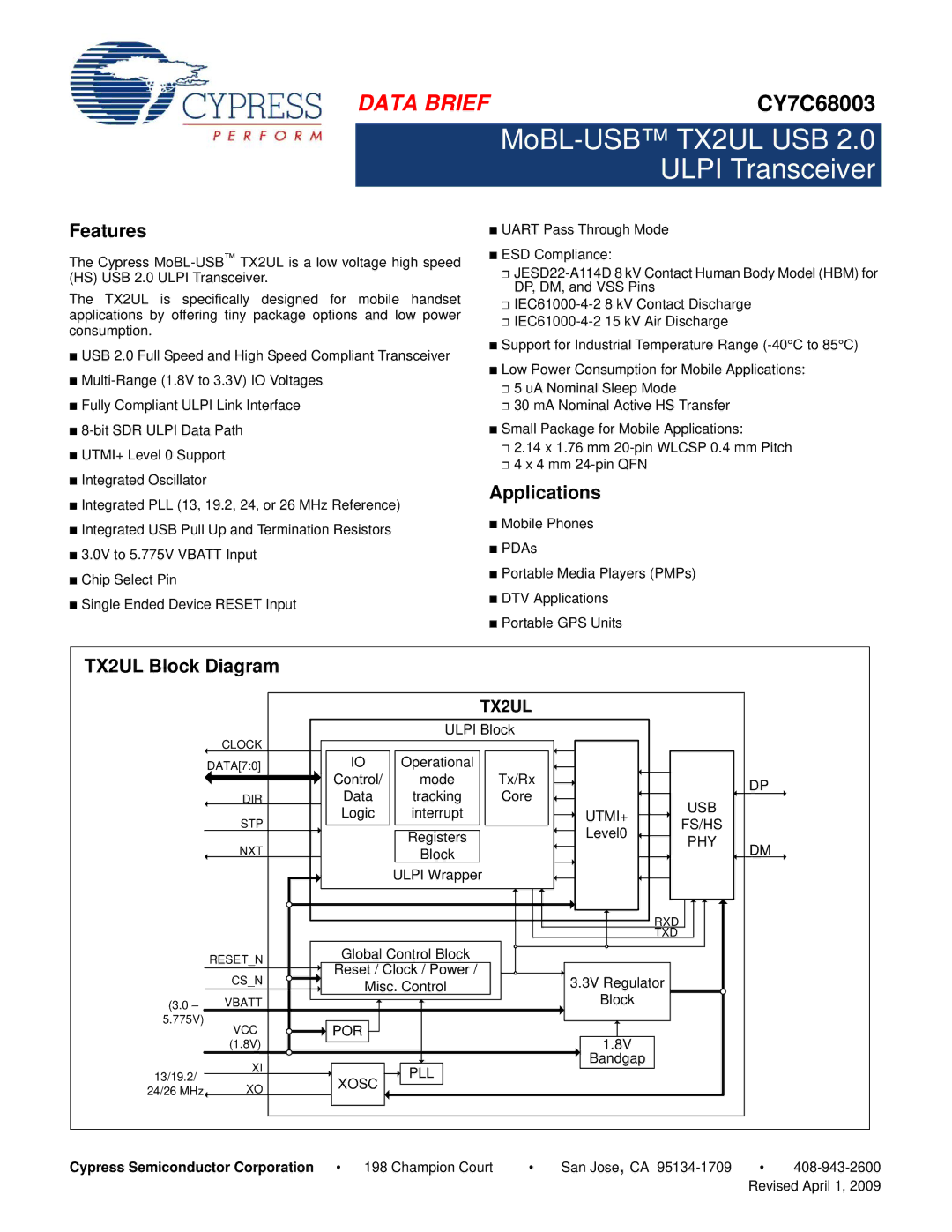

TX2UL Block Diagram

|

|

|

| TX2UL |

|

|

|

| |

| CLOCK |

|

| ULPI Block |

|

|

|

| |

|

|

|

|

|

|

|

|

| |

| DATA[7:0] |

| IO | Operational | Tx/Rx |

|

|

|

|

|

| Control/ | mode |

|

| DP |

| ||

| DIR |

| Data | tracking | Core |

|

|

| |

|

|

| USB |

|

| ||||

|

|

| Logic | interrupt |

| UTMI+ |

|

| |

| STP |

|

| FS/HS |

|

| |||

|

|

| Registers |

| Level0 |

|

| ||

| NXT |

|

|

| PHY | DM |

| ||

|

|

| Block |

|

|

|

| ||

|

|

|

| ULPI Wrapper |

|

|

|

|

|

|

|

|

|

|

| RXD |

|

|

|

|

|

|

|

|

| TXD |

|

|

|

| RESET_N |

| Global Control Block |

|

|

|

|

| |

| Reset / Clock / Power / |

|

|

|

|

| |||

| CS_N |

| 3.3V Regulator |

|

|

| |||

|

| Misc. Control |

|

|

|

| |||

(3.0 – | VBATT |

|

|

|

| Block |

|

|

|

5.775V) | VCC | POR |

|

|

|

|

|

| |

|

|

| 1.8V |

|

|

| |||

| (1.8V) |

|

|

|

|

|

|

| |

| XI |

|

| PLL |

| Bandgap |

|

|

|

13/19.2/ | XOSC |

|

|

|

|

| |||

XO |

|

|

|

|

| ||||

24/26 MHz |

|

|

|

|

|

| |||

|

|

|

|

|

|

|

| ||

Cypress Semiconductor Corporation | • | 198 Champion Court | • | San Jose, CA | • | ||||

Revised April 1, 2009