|

|

|

|

|

|

|

|

| STK11C88 | |

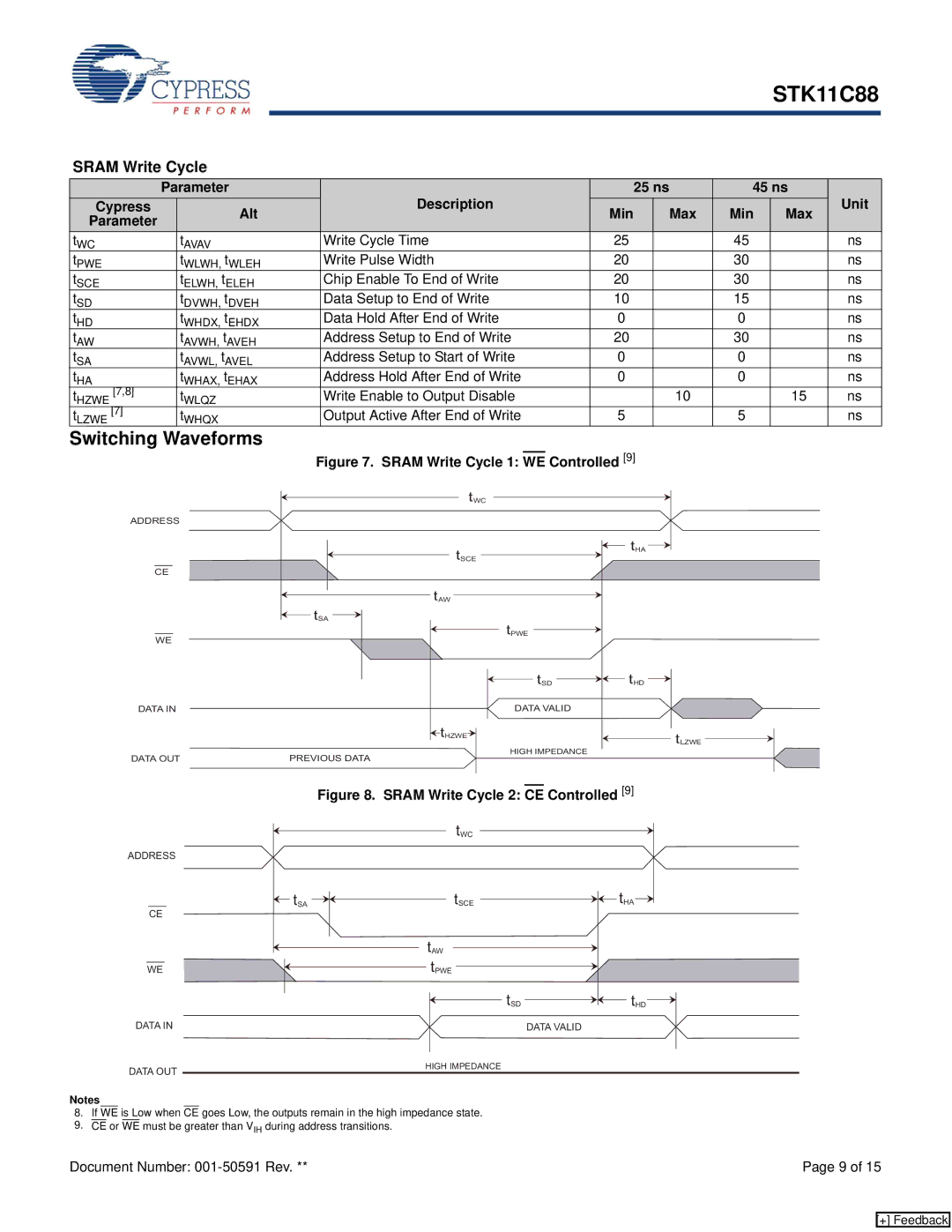

SRAM Write Cycle |

|

|

|

|

|

|

|

| ||

| Parameter |

| Description |

| 25 ns | 45 ns | Unit | |||

Cypress |

| Alt |

| Min |

| Max | Min | Max | ||

Parameter |

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

| |

tWC |

| tAVAV |

| Write Cycle Time | 25 |

|

| 45 |

| ns |

tPWE |

| tWLWH, tWLEH |

| Write Pulse Width | 20 |

|

| 30 |

| ns |

tSCE |

| tELWH, tELEH |

| Chip Enable To End of Write | 20 |

|

| 30 |

| ns |

tSD |

| tDVWH, tDVEH |

| Data Setup to End of Write | 10 |

|

| 15 |

| ns |

tHD |

| tWHDX, tEHDX |

| Data Hold After End of Write | 0 |

|

| 0 |

| ns |

tAW |

| tAVWH, tAVEH |

| Address Setup to End of Write | 20 |

|

| 30 |

| ns |

tSA |

| tAVWL, tAVEL |

| Address Setup to Start of Write | 0 |

|

| 0 |

| ns |

tHA |

| tWHAX, tEHAX |

| Address Hold After End of Write | 0 |

|

| 0 |

| ns |

tHZWE [7,8] |

| tWLQZ |

| Write Enable to Output Disable |

|

| 10 |

| 15 | ns |

tLZWE [7] |

| tWHQX |

| Output Active After End of Write | 5 |

|

| 5 |

| ns |

Switching Waveforms

Figure 7. SRAM Write Cycle 1: WE Controlled [9]

| tWC |

ADDRESS |

|

| tSCE |

CE |

|

| tAW |

| tSA |

WE | tPWE |

| |

| tSD |

DATA IN | DATA VALID |

| tHZWE |

| HIGH IMPEDANCE |

DATA OUT | PREVIOUS DATA |

tHA

tHD

tLZWE

Figure 8. SRAM Write Cycle 2: CE Controlled [9]

ADDRESS

CE

WE

DATA IN

DATA OUT

tWC

tSA |

|

|

| tSCE |

|

|

| tHA |

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

tAW

tPWE

tSD ![]()

![]() tHD

tHD![]()

DATA VALID

HIGH IMPEDANCE

Notes

8.If WE is Low when CE goes Low, the outputs remain in the high impedance state.

9.CE or WE must be greater than VIH during address transitions.

Document Number: | Page 9 of 15 |

[+] Feedback