Chapter 3 Programming

The PIB contains ISA Bridge I/O Registers for various functions. These registers are accessible from the PCI bus.

Super I/O

The Super I/O device provides the following functions:

■Two serial ports (asynchronous)

■Parallel port interface

The device’s hardware configuration is based on two

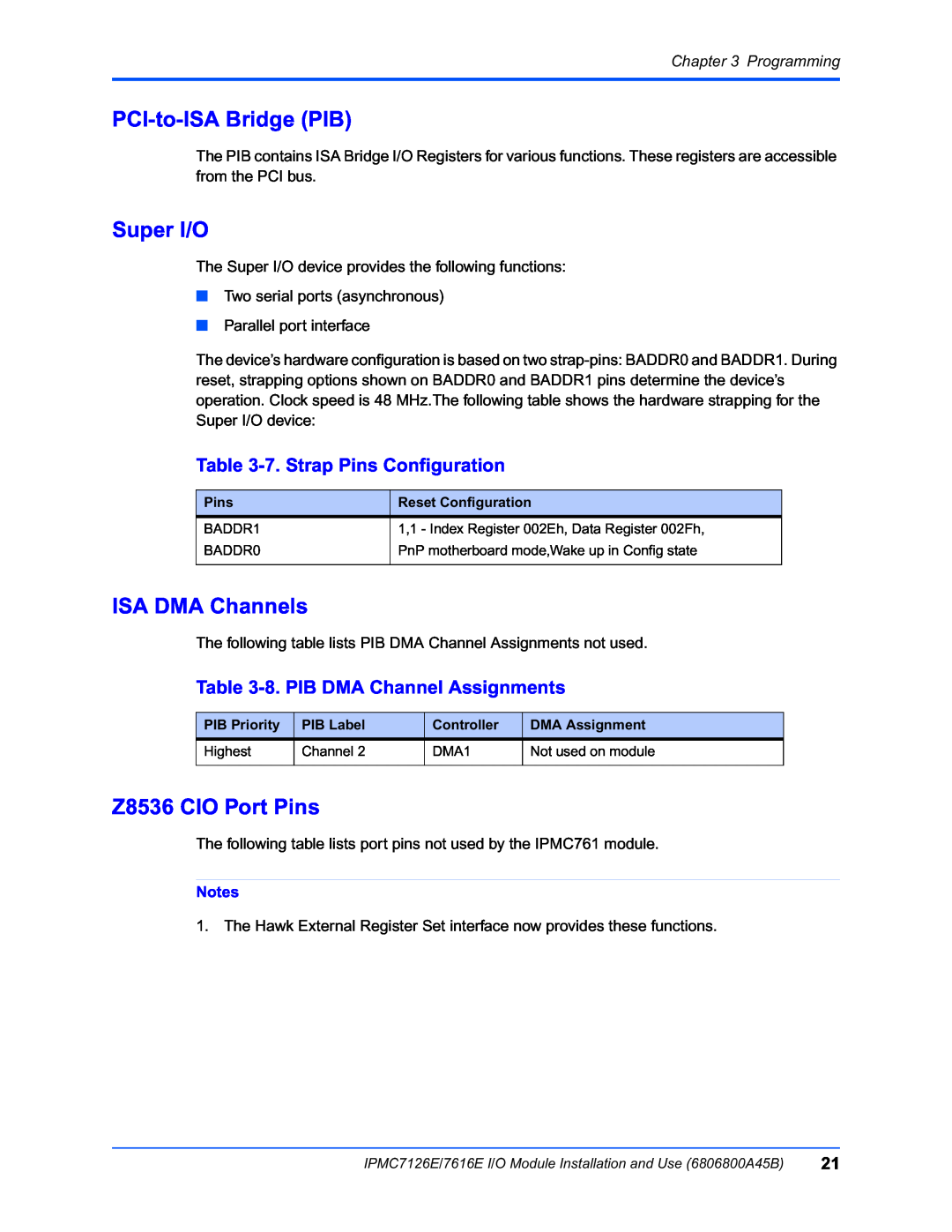

Table 3-7. Strap Pins Configuration

Pins

BADDR1

BADDR0

Reset Configuration

1,1 - Index Register 002Eh, Data Register 002Fh,

PnP motherboard mode,Wake up in Config state

ISA DMA Channels

The following table lists PIB DMA Channel Assignments not used.

Table 3-8. PIB DMA Channel Assignments

PIB Priority | PIB Label | Controller | DMA Assignment |

Highest | Channel 2 | DMA1 | Not used on module |

|

|

|

|

Z8536 CIO Port Pins

The following table lists port pins not used by the IPMC761 module.

Notes

1. The Hawk External Register Set interface now provides these functions.

IPMC7126E/7616E I/O Module Installation and Use (6806800A45B) | 21 |