English

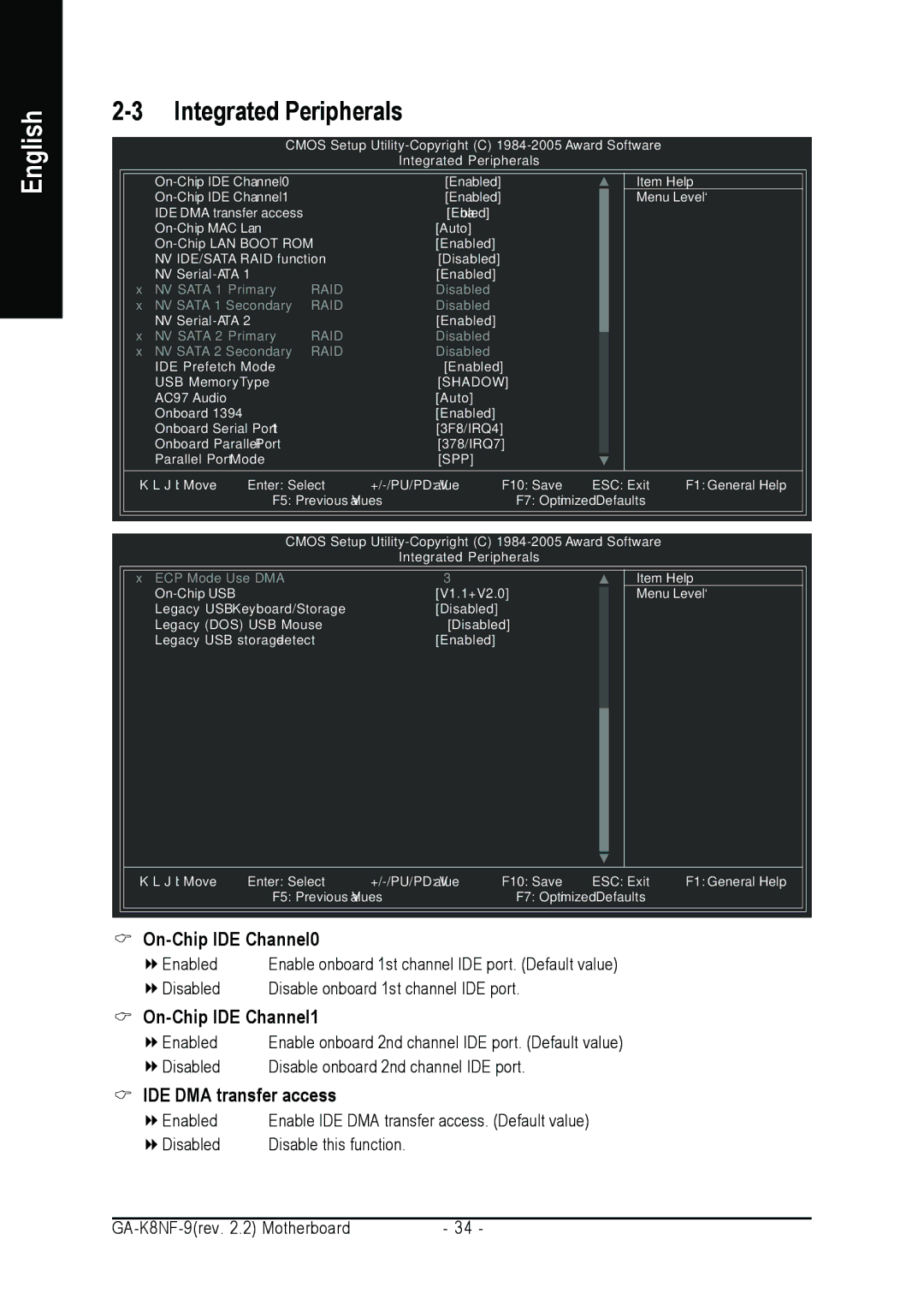

2-3 Integrated Peripherals

CMOS Setup

Integrated Peripherals

|

| [Enabled] | |

|

| [Enabled] | |

| IDE DMA transfer access |

| [Enabled] |

|

| [Auto] | |

|

| [Enabled] | |

| NV IDE/SATA RAID function | [Disabled] | |

| NV |

| [Enabled] |

x | NV SATA 1 Primary | RAID | Disabled |

x | NV SATA 1 Secondary | RAID | Disabled |

| NV |

| [Enabled] |

x | NV SATA 2 Primary | RAID | Disabled |

x | NV SATA 2 Secondary | RAID | Disabled |

| IDE Prefetch Mode |

| [Enabled] |

| USB Memory Type |

| [SHADOW] |

| AC97 Audio |

| [Auto] |

| Onboard 1394 |

| [Enabled] |

| Onboard Serial Port 1 |

| [3F8/IRQ4] |

| Onboard Parallel Port |

| [378/IRQ7] |

| Parallel Port Mode |

| [SPP] |

Item Help

Menu Level`

KLJI: Move | Enter: Select | F10: Save | ESC: Exit | F1: General Help | ||||

| F5: Previous Values |

| F7: Optimized Defaults |

| ||||

| CMOS Setup |

| ||||||

|

|

| Integrated Peripherals |

|

|

|

| |

x ECP Mode Use DMA |

| 3 |

|

|

| Item Help | ||

|

| [V1.1+V2.0] |

|

| Menu Level` | |||

Legacy USB Keyboard/Storage |

| [Disabled] |

|

|

|

|

| |

Legacy (DOS) USB Mouse |

| [Disabled] |

|

|

|

|

| |

Legacy USB storage detect |

| [Enabled] |

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

KLJI: Move | Enter: Select | F10: Save | ESC: Exit | F1: General Help | |

| F5: Previous Values | F7: Optimized Defaults |

| ||

On-Chip IDE Channel0

Enabled | Enable onboard 1st channel IDE port. (Default value) |

Disabled | Disable onboard 1st channel IDE port. |

On-Chip IDE Channel1

Enabled | Enable onboard 2nd channel IDE port. (Default value) |

Disabled | Disable onboard 2nd channel IDE port. |

IDE DMA transfer access

Enabled | Enable IDE DMA transfer access. (Default value) |

Disabled | Disable this function. |

- 34 - |