System Support

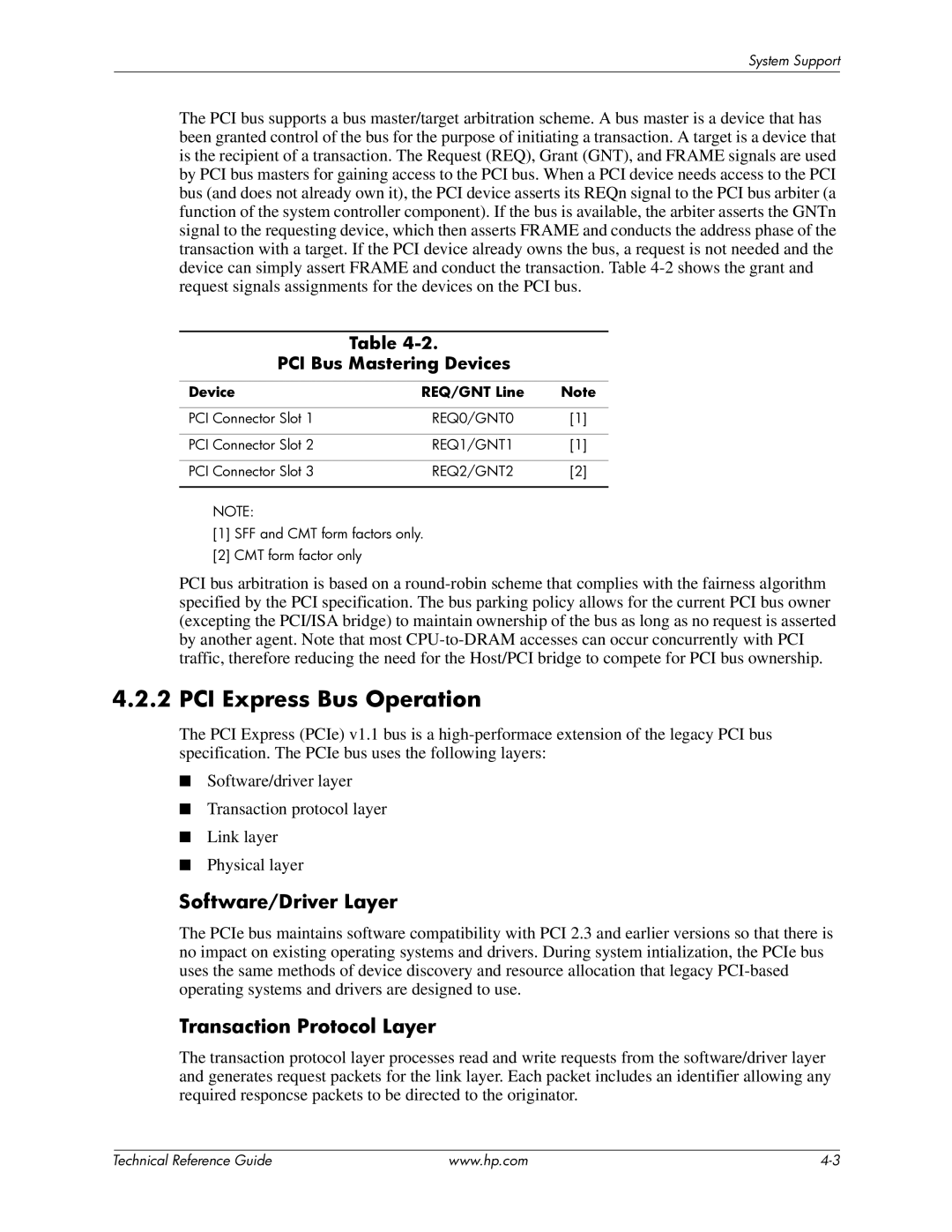

The PCI bus supports a bus master/target arbitration scheme. A bus master is a device that has been granted control of the bus for the purpose of initiating a transaction. A target is a device that is the recipient of a transaction. The Request (REQ), Grant (GNT), and FRAME signals are used by PCI bus masters for gaining access to the PCI bus. When a PCI device needs access to the PCI bus (and does not already own it), the PCI device asserts its REQn signal to the PCI bus arbiter (a function of the system controller component). If the bus is available, the arbiter asserts the GNTn signal to the requesting device, which then asserts FRAME and conducts the address phase of the transaction with a target. If the PCI device already owns the bus, a request is not needed and the device can simply assert FRAME and conduct the transaction. Table

Table

PCI Bus Mastering Devices

Device | REQ/GNT Line | Note |

|

|

|

PCI Connector Slot 1 | REQ0/GNT0 | [1] |

|

|

|

PCI Connector Slot 2 | REQ1/GNT1 | [1] |

|

|

|

PCI Connector Slot 3 | REQ2/GNT2 | [2] |

|

|

|

NOTE:

[1]SFF and CMT form factors only.

[2]CMT form factor only

PCI bus arbitration is based on a

4.2.2 PCI Express Bus Operation

The PCI Express (PCIe) v1.1 bus is a

■Software/driver layer

■Transaction protocol layer

■Link layer

■Physical layer

Software/Driver Layer

The PCIe bus maintains software compatibility with PCI 2.3 and earlier versions so that there is no impact on existing operating systems and drivers. During system intialization, the PCIe bus uses the same methods of device discovery and resource allocation that legacy

Transaction Protocol Layer

The transaction protocol layer processes read and write requests from the software/driver layer and generates request packets for the link layer. Each packet includes an identifier allowing any required responcse packets to be directed to the originator.

| Technical Reference Guide | www.hp.com |