BIOS SETUP

Advanced Chipset Features

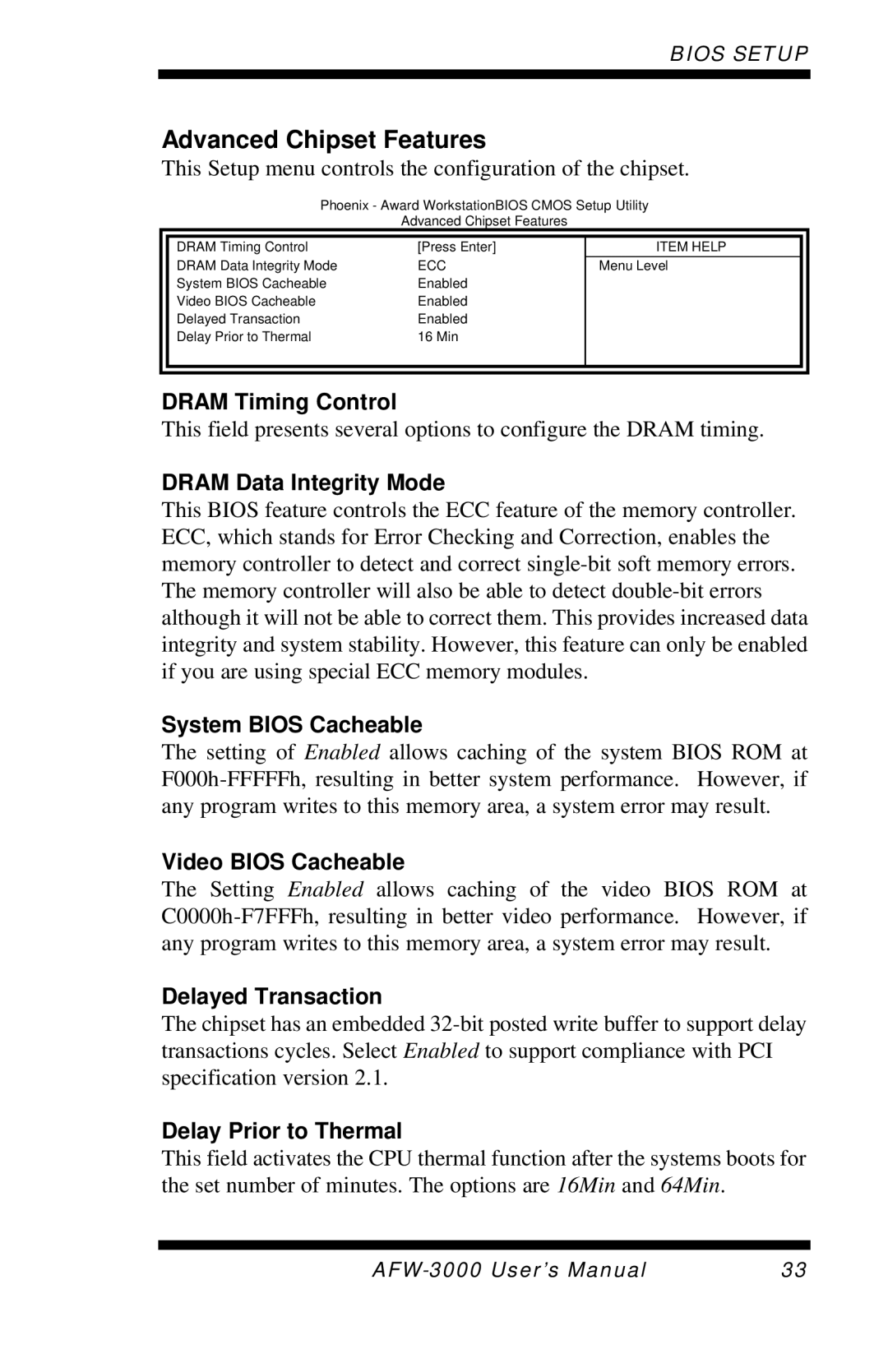

This Setup menu controls the configuration of the chipset.

Phoenix - Award WorkstationBIOS CMOS Setup Utility

Advanced Chipset Features

|

|

|

|

|

| DRAM Timing Control | [Press Enter] | ITEM HELP |

|

| DRAM Data Integrity Mode | ECC | Menu Level |

|

| System BIOS Cacheable | Enabled |

|

|

| Video BIOS Cacheable | Enabled |

|

|

| Delayed Transaction | Enabled |

|

|

| Delay Prior to Thermal | 16 Min |

|

|

|

|

|

|

|

|

|

|

|

|

DRAM Timing Control

This field presents several options to configure the DRAM timing.

DRAM Data Integrity Mode

This BIOS feature controls the ECC feature of the memory controller. ECC, which stands for Error Checking and Correction, enables the memory controller to detect and correct

System BIOS Cacheable

The setting of Enabled allows caching of the system BIOS ROM at

Video BIOS Cacheable

The Setting Enabled allows caching of the video BIOS ROM at

Delayed Transaction

The chipset has an embedded

Delay Prior to Thermal

This field activates the CPU thermal function after the systems boots for the set number of minutes. The options are 16Min and 64Min.

33 |