Intel® LXD972M Transceiver Demo Board (Board Rev A1)

2.4.5CFG Pin Configuration Options

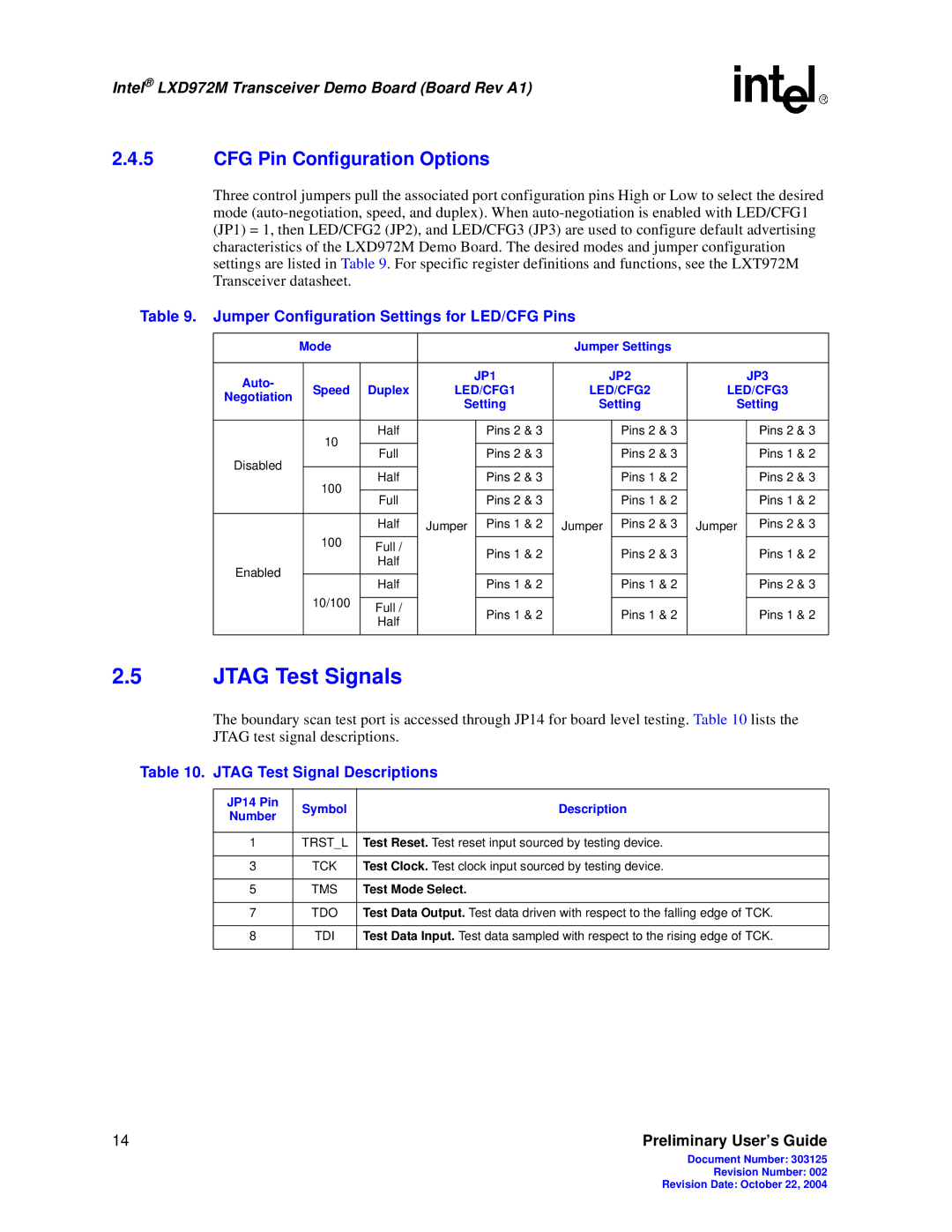

Three control jumpers pull the associated port configuration pins High or Low to select the desired mode

Table 9. Jumper Configuration Settings for LED/CFG Pins

| Mode |

|

|

| Jumper Settings |

|

| ||

|

|

|

|

|

|

|

|

|

|

Auto- |

|

|

| JP1 | JP2 |

| JP3 | ||

| Speed | Duplex | LED/CFG1 | LED/CFG2 | LED/CFG3 | ||||

Negotiation |

| ||||||||

|

|

| Setting | Setting | Setting | ||||

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

| 10 | Half |

| Pins 2 & 3 |

| Pins 2 & 3 |

| Pins 2 & 3 |

|

|

|

|

|

|

|

|

| |

Disabled |

| Full |

| Pins 2 & 3 |

| Pins 2 & 3 |

| Pins 1 & 2 | |

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

| |

| 100 | Half |

| Pins 2 & 3 |

| Pins 1 & 2 |

| Pins 2 & 3 | |

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

| |

|

| Full |

| Pins 2 & 3 |

| Pins 1 & 2 |

| Pins 1 & 2 | |

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

| Half | Jumper | Pins 1 & 2 | Jumper | Pins 2 & 3 | Jumper | Pins 2 & 3 |

|

| 100 |

|

|

|

|

|

|

|

|

| Full / |

| Pins 1 & 2 |

| Pins 2 & 3 |

| Pins 1 & 2 | |

|

|

|

|

|

| ||||

|

|

| Half |

|

|

| |||

Enabled |

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

| |

|

| Half |

| Pins 1 & 2 |

| Pins 1 & 2 |

| Pins 2 & 3 | |

|

|

|

|

|

| ||||

|

| 10/100 |

|

|

|

|

|

|

|

|

| Full / |

| Pins 1 & 2 |

| Pins 1 & 2 |

| Pins 1 & 2 | |

|

|

|

|

|

| ||||

|

|

| Half |

|

|

| |||

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

2.5JTAG Test Signals

The boundary scan test port is accessed through JP14 for board level testing. Table 10 lists the JTAG test signal descriptions.

Table 10. JTAG Test Signal Descriptions

JP14 Pin | Symbol | Description | |

Number | |||

|

| ||

|

|

| |

1 | TRST_L | Test Reset. Test reset input sourced by testing device. | |

|

|

| |

3 | TCK | Test Clock. Test clock input sourced by testing device. | |

|

|

| |

5 | TMS | Test Mode Select. | |

|

|

| |

7 | TDO | Test Data Output. Test data driven with respect to the falling edge of TCK. | |

|

|

| |

8 | TDI | Test Data Input. Test data sampled with respect to the rising edge of TCK. | |

|

|

|

14 | Preliminary User’s Guide |

Document Number: 303125

Revision Number: 002

Revision Date: October 22, 2004