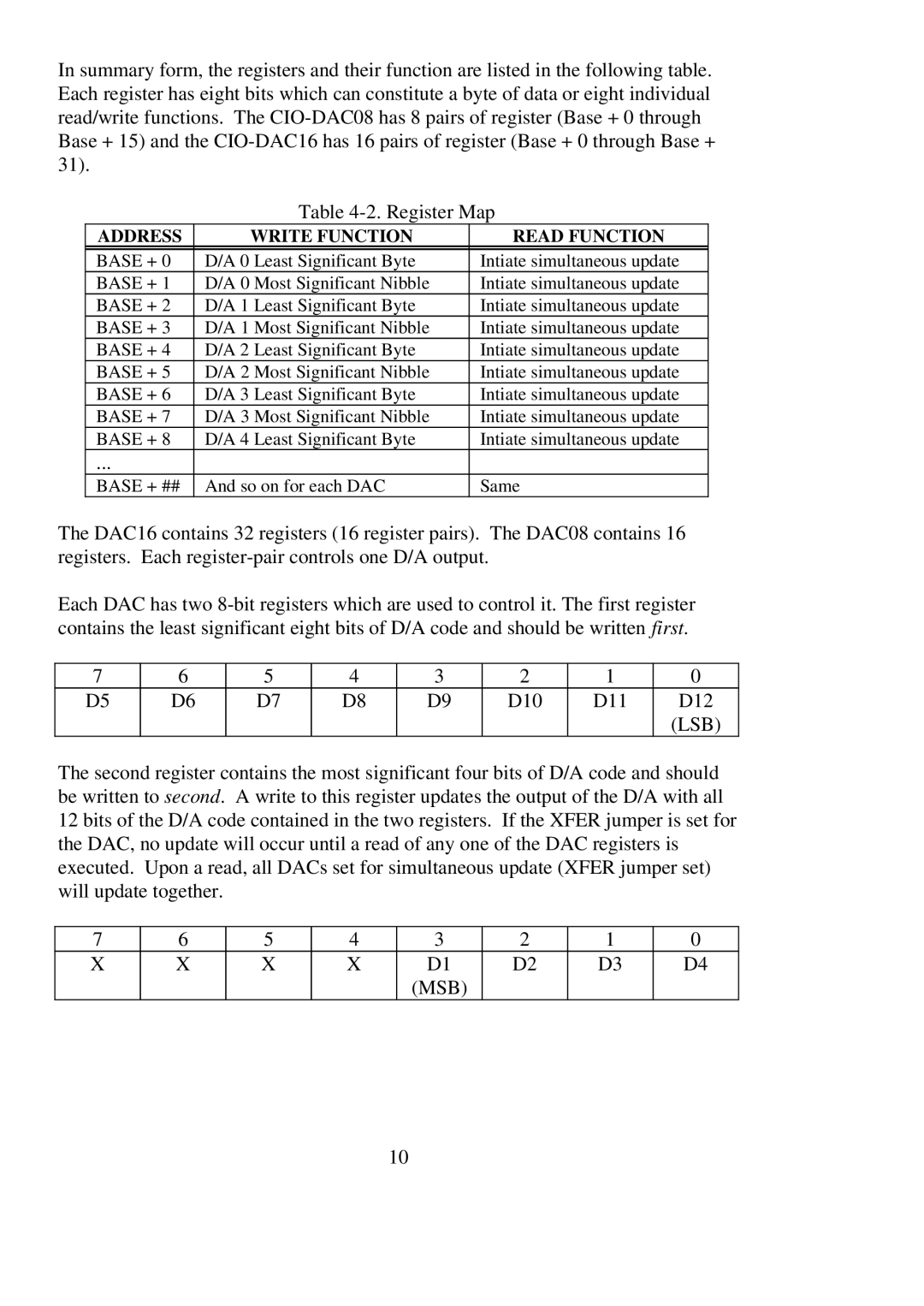

In summary form, the registers and their function are listed in the following table. Each register has eight bits which can constitute a byte of data or eight individual read/write functions. The

Table

ADDRESS | WRITE FUNCTION | READ FUNCTION |

|

|

|

BASE + 0 | D/A 0 Least Significant Byte | Intiate simultaneous update |

BASE + 1 | D/A 0 Most Significant Nibble | Intiate simultaneous update |

BASE + 2 | D/A 1 Least Significant Byte | Intiate simultaneous update |

BASE + 3 | D/A 1 Most Significant Nibble | Intiate simultaneous update |

BASE + 4 | D/A 2 Least Significant Byte | Intiate simultaneous update |

BASE + 5 | D/A 2 Most Significant Nibble | Intiate simultaneous update |

BASE + 6 | D/A 3 Least Significant Byte | Intiate simultaneous update |

BASE + 7 | D/A 3 Most Significant Nibble | Intiate simultaneous update |

BASE + 8 | D/A 4 Least Significant Byte | Intiate simultaneous update |

... |

|

|

BASE + ## | And so on for each DAC | Same |

The DAC16 contains 32 registers (16 register pairs). The DAC08 contains 16 registers. Each

Each DAC has two

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

D5 | D6 | D7 | D8 | D9 | D10 | D11 | D12 |

|

|

|

|

|

|

| (LSB) |

The second register contains the most significant four bits of D/A code and should be written to second. A write to this register updates the output of the D/A with all 12 bits of the D/A code contained in the two registers. If the XFER jumper is set for the DAC, no update will occur until a read of any one of the DAC registers is executed. Upon a read, all DACs set for simultaneous update (XFER jumper set) will update together.

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

X | X | X | X | D1 | D2 | D3 | D4 |

|

|

|

| (MSB) |

|

|

|

10