5 | 6 | 7 | 8 |

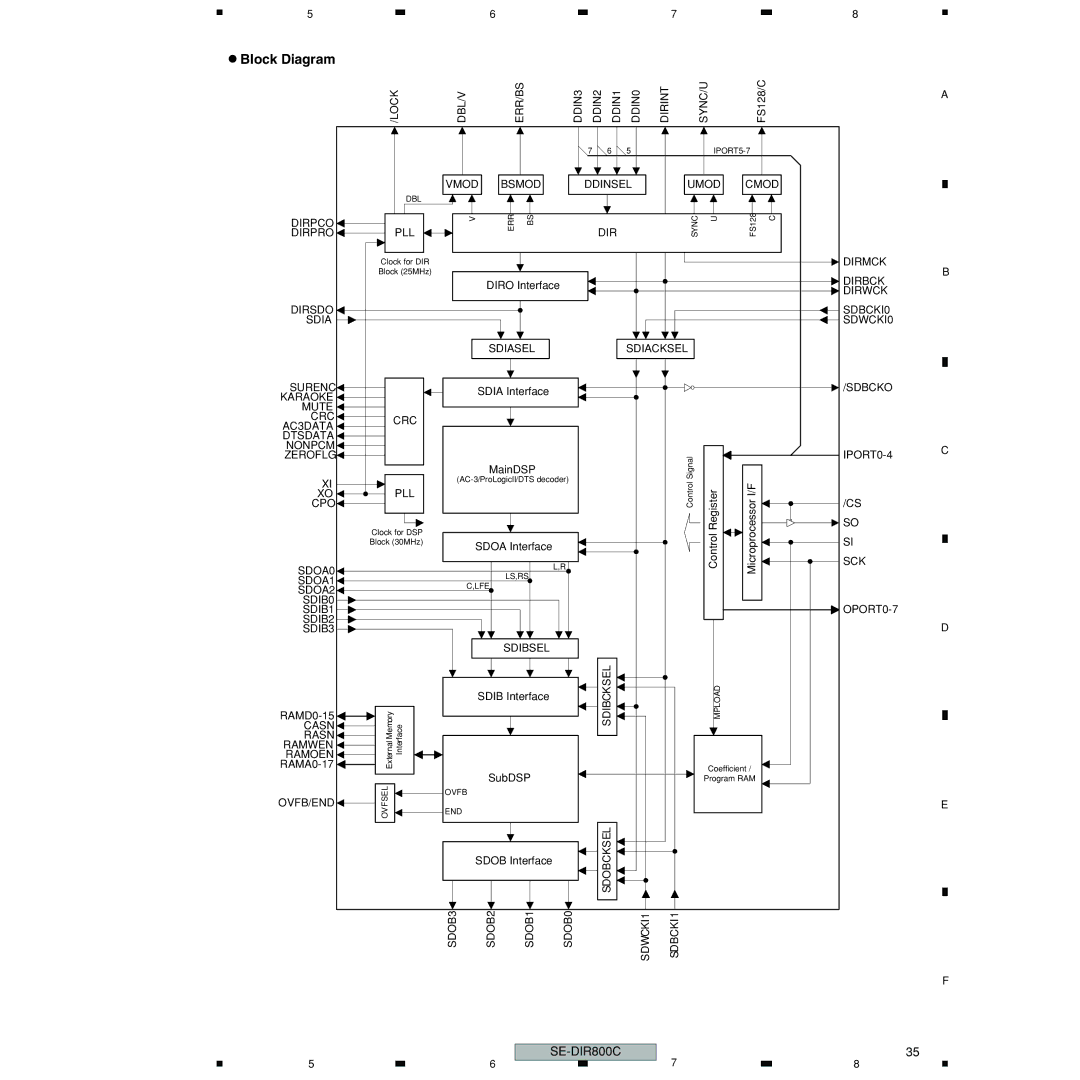

Block Diagram

Block Diagram

| /LOCK | DBL/V |

| ERR/BS |

| DDIN3 | DDIN2 DDIN1 | DDIN0 | DIRINT | SYNC/U |

| FS128/C |

| A |

|

|

|

|

|

| |||||||||

|

|

|

|

|

| 7 | 6 | 5 |

|

|

|

| ||

|

| VMOD | BSMOD |

| DDINSEL | UMOD | CMOD |

|

| |||||

| DBL |

|

|

|

|

|

|

|

|

|

|

|

|

|

DIRPCO |

| V | ERR | BS |

|

|

|

| SYNC | U | FS128 | C |

|

|

DIRPRO | PLL |

|

| DIR |

|

|

| |||||||

| Clock for DIR |

|

|

|

|

|

|

|

|

|

|

| DIRMCK | B |

| Block (25MHz) |

|

|

|

|

|

|

|

|

|

|

| DIRBCK | |

|

|

| DIRO Interface |

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

| DIRWCK |

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

DIRSDO |

|

|

|

|

|

|

|

|

|

|

|

| SDBCKI0 |

|

SDIA |

|

|

|

|

|

|

|

|

|

|

|

| SDWCKI0 |

|

|

|

| SDIASEL |

|

|

| SDIACKSEL |

|

|

|

|

| ||

SURENC |

| SDIA Interface |

|

|

|

|

|

|

|

| /SDBCKO |

| ||

KARAOKE |

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

MUTE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CRC | CRC |

|

|

|

|

|

|

|

|

|

|

|

|

|

AC3DATA |

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

DTSDATA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NONPCM |

|

|

|

|

|

|

|

|

|

|

|

|

| C |

ZEROFLG |

|

|

|

|

|

|

|

| Signal |

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

| MainDSP |

|

|

|

|

|

|

|

|

| ||

XI |

|

|

|

|

|

|

|

|

| |||||

|

|

|

| Control |

| Microprocessor I/F |

|

|

| |||||

PLL |

|

|

|

|

|

|

|

|

|

|

| |||

XO |

|

|

|

|

|

|

| Control Register |

| /CS |

| |||

CPO |

|

|

|

|

|

|

|

|

|

| ||||

| Clock for DSP |

|

|

|

|

|

|

|

| SO |

| |||

|

|

|

|

|

|

|

|

| SI |

| ||||

| Block (30MHz) | SDOA Interface |

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

| ||||||

SDOA0 |

|

|

|

| L,R |

|

|

|

| SCK |

| |||

|

|

|

|

|

|

|

|

|

| |||||

|

| LS,RS |

|

|

|

|

|

|

| |||||

SDOA1 |

|

|

|

|

|

|

|

|

|

|

|

| ||

| C,LFE |

|

|

|

|

|

|

|

|

|

|

| ||

SDOA2 |

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

SDIB0 |

|

|

|

|

|

|

|

|

|

|

|

|

| |

SDIB1 |

|

|

|

|

|

|

|

|

|

|

|

|

| |

SDIB2 |

|

|

|

|

|

|

|

|

|

|

|

|

| D |

SDIB3 |

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

| SDIBSEL |

|

|

|

|

|

|

|

|

|

| |

|

| SDIB Interface |

|

| SDIBCKSEL |

|

| MPLOAD |

|

|

|

| ||

ExternalMemory Interface |

|

|

|

|

|

|

|

|

|

|

| |||

CASN |

|

|

|

|

|

|

|

|

|

|

| |||

RASN |

|

|

|

|

|

|

|

|

|

|

| |||

RAMWEN |

|

|

|

|

|

|

|

|

|

|

| |||

RAMOEN |

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

| SubDSP |

|

|

|

|

| Coefficient / |

|

|

| ||

|

|

|

|

|

|

|

| Program RAM |

|

|

| |||

OVFB/END | OVFSEL | OVFB |

|

|

|

|

|

|

|

|

|

|

|

|

END |

|

|

|

|

|

|

|

|

|

|

| E | ||

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

| SDOB Interface |

|

| SDOBCKSEL |

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

| SDOB3 | SDOB2 | SDOB1 | SDOB0 |

|

| SDWCKI1 | SDBCKI1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| F |

5 |

|

| 6 |

| 7 |

|

|

| 8 | 35 | ||||

|

|

|

|

|

|

|

|

|

|

| ||||