|

| 5 |

|

| 6 | 7 | 8 |

|

|

|

|

|

|

|

|

|

|

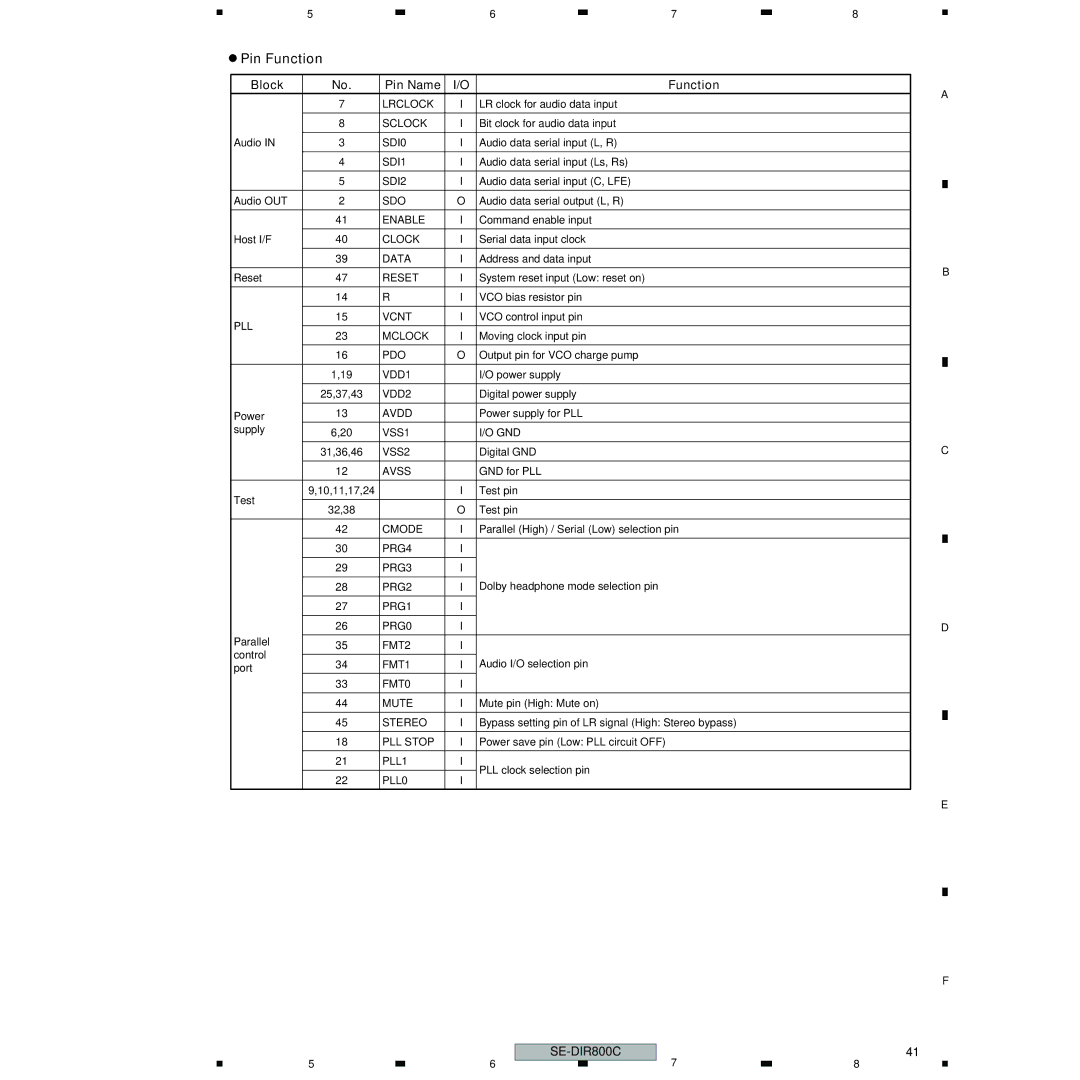

| Pin Function |

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

| Block | No. | Pin Name | I/O |

| Function |

|

|

|

| 7 | LRCLOCK | I | LR clock for audio data input |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 8 | SCLOCK | I | Bit clock for audio data input |

|

|

|

| Audio IN |

|

|

|

|

|

|

|

| 3 | SDI0 | I | Audio data serial input (L, R) |

|

|

| |

|

|

|

|

|

|

|

|

|

|

| 4 | SDI1 | I | Audio data serial input (Ls, Rs) |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 5 | SDI2 | I | Audio data serial input (C, LFE) |

|

|

|

|

|

|

|

|

|

|

|

|

| Audio OUT | 2 | SDO | O | Audio data serial output (L, R) |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 41 | ENABLE | I | Command enable input |

|

|

|

|

|

|

|

|

|

|

|

|

| Host I/F | 40 | CLOCK | I | Serial data input clock |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 39 | DATA | I | Address and data input |

|

|

|

|

|

|

|

|

|

|

|

|

| Reset | 47 | RESET | I | System reset input (Low: reset on) |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 14 | R | I | VCO bias resistor pin |

|

|

|

|

|

|

|

|

|

|

|

|

| PLL | 15 | VCNT | I | VCO control input pin |

|

|

|

|

|

|

|

|

|

|

| |

| 23 | MCLOCK | I | Moving clock input pin |

|

|

| |

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

| 16 | PDO | O | Output pin for VCO charge pump |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1,19 | VDD1 | − | I/O power supply |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 25,37,43 | VDD2 | − | Digital power supply |

|

|

|

|

|

|

|

|

|

|

|

|

| Power | 13 | AVDD | − | Power supply for PLL |

|

|

|

| supply | 6,20 | VSS1 | − | I/O GND |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 31,36,46 | VSS2 | − | Digital GND |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 12 | AVSS | − | GND for PLL |

|

|

|

|

|

|

|

|

|

|

|

|

| Test | 9,10,11,17,24 |

| I | Test pin |

|

|

|

|

|

|

|

|

|

|

| |

| 32,38 |

| O | Test pin |

|

|

| |

|

|

|

|

|

| |||

|

|

|

|

|

|

|

| |

|

| 42 | CMODE | I | Parallel (High) / Serial (Low) selection pin |

|

| |

|

|

|

|

|

|

|

|

|

|

| 30 | PRG4 | I |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 29 | PRG3 | I |

|

|

|

|

|

|

|

|

| Dolby headphone mode selection pin |

|

|

|

|

| 28 | PRG2 | I |

|

|

| |

|

|

|

|

|

|

|

|

|

|

| 27 | PRG1 | I |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 26 | PRG0 | I |

|

|

|

|

| Parallel |

|

|

|

|

|

|

|

| 35 | FMT2 | I |

|

|

|

| |

| control |

|

|

|

| |||

|

|

|

| Audio I/O selection pin |

|

|

| |

| 34 | FMT1 | I |

|

|

| ||

| port |

|

|

| ||||

|

| 33 | FMT0 | I |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 44 | MUTE | I | Mute pin (High: Mute on) |

|

|

|

|

|

|

|

|

|

|

| |

|

| 45 | STEREO | I | Bypass setting pin of LR signal (High: Stereo bypass) |

|

| |

|

|

|

|

|

|

|

|

|

|

| 18 | PLL STOP | I | Power save pin (Low: PLL circuit OFF) |

|

|

|

|

|

|

|

|

|

|

|

|

|

| 21 | PLL1 | I | PLL clock selection pin |

|

|

|

|

|

|

|

|

|

|

| |

|

| 22 | PLL0 | I |

|

|

| |

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A

B

C

D

E

F

5 | 6 |

41

7 | 8 |