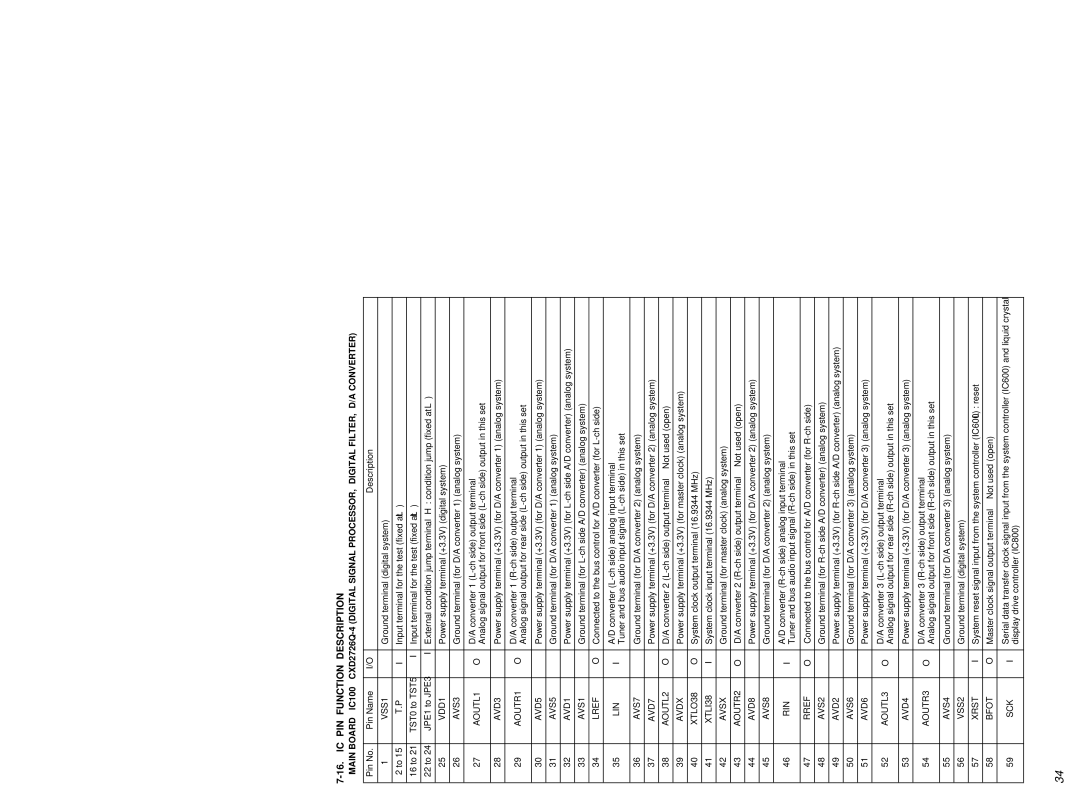

7-16. IC PIN FUNCTION DESCRIPTION

•MAIN BOARD IC100

Pin No. |

| Pin Name | I/O |

| Description | ||

|

|

|

|

|

|

|

|

1 |

| VSS1 | — | Ground terminal (digital system) |

|

| |

|

|

|

|

|

|

| |

2 to 15 |

| T.P | I | Input terminal for the test (fixed at “L”) |

| ||

|

|

|

|

|

|

| |

16 to 21 | TST0 to TST5 | I | Input terminal for the test (fixed at “L”) |

| |||

|

|

|

|

|

|

| |

22 to 24 | JPE1 to JPE3 | I | External condition jump terminal | “H”: condition jump (fixed at “L”) | |||

|

|

|

|

|

| ||

25 |

| VDD1 | — | Power supply terminal (+3.3V) (digital system) | |||

|

|

|

|

|

| ||

26 |

| AVS3 | — | Ground terminal (for D/A converter 1) (analog system) | |||

|

|

|

|

|

|

| |

27 |

| AOUTL1 | O | D/A converter 1 |

| ||

| Analog signal output for front side | ||||||

|

|

|

|

| |||

|

|

|

|

|

| ||

28 |

| AVD3 | — | Power supply terminal (+3.3V) (for D/A converter 1) (analog system) | |||

|

|

|

|

|

|

| |

29 |

| AOUTR1 | O | D/A converter 1 |

| ||

| Analog signal output for rear side | ||||||

|

|

|

|

| |||

|

|

|

|

|

| ||

30 |

| AVD5 | — | Power supply terminal (+3.3V) (for D/A converter 1) (analog system) | |||

|

|

|

|

|

| ||

31 |

| AVS5 | — | Ground terminal (for D/A converter 1) (analog system) | |||

|

|

|

|

|

| ||

32 |

| AVD1 | — | Power supply terminal (+3.3V) (for | |||

|

|

|

|

|

| ||

33 |

| AVS1 | — | Ground terminal (for | |||

|

|

|

|

|

| ||

34 |

| LREF | O | Connected to the bus control for A/D converter (for | |||

|

|

|

|

|

| ||

35 |

| LIN | I | A/D converter | |||

| Tuner and bus audio input signal | ||||||

|

|

|

|

| |||

|

|

|

|

|

| ||

36 |

| AVS7 | — | Ground terminal (for D/A converter 2) (analog system) | |||

|

|

|

|

|

| ||

37 |

| AVD7 | — | Power supply terminal (+3.3V) (for D/A converter 2) (analog system) | |||

|

|

|

|

|

|

| |

38 |

| AOUTL2 | O | D/A converter 2 | Not used (open) | ||

|

|

|

|

|

| ||

39 |

| AVDX | — | Power supply terminal (+3.3V) (for master clock) (analog system) | |||

|

|

|

|

|

|

| |

40 |

| XTLO38 | O | System clock output terminal (16.9344 MHz) |

| ||

|

|

|

|

|

|

| |

41 |

| XTLI38 | I | System clock input terminal (16.9344 MHz) |

| ||

|

|

|

|

|

| ||

42 |

| AVSX | — | Ground terminal (for master clock) (analog system) | |||

|

|

|

|

|

|

| |

43 |

| AOUTR2 | O | D/A converter 2 | Not used (open) | ||

|

|

|

|

|

| ||

44 |

| AVD8 | — | Power supply terminal (+3.3V) (for D/A converter 2) (analog system) | |||

|

|

|

|

|

| ||

45 |

| AVS8 | — | Ground terminal (for D/A converter 2) (analog system) | |||

|

|

|

|

|

| ||

46 |

| RIN | I | A/D converter | |||

| Tuner and bus audio input signal | ||||||

|

|

|

|

| |||

|

|

|

|

|

| ||

47 |

| RREF | O | Connected to the bus control for A/D converter (for | |||

|

|

|

|

|

| ||

48 |

| AVS2 | — | Ground terminal (for | |||

|

|

|

|

|

| ||

49 |

| AVD2 | — | Power supply terminal (+3.3V) (for | |||

|

|

|

|

|

| ||

50 |

| AVS6 | — | Ground terminal (for D/A converter 3) (analog system) | |||

|

|

|

|

|

| ||

51 |

| AVD6 | — | Power supply terminal (+3.3V) (for D/A converter 3) (analog system) | |||

|

|

|

|

|

|

| |

52 |

| AOUTL3 | O | D/A converter 3 |

| ||

| Analog signal output for rear side | ||||||

|

|

|

|

| |||

|

|

|

|

|

| ||

53 |

| AVD4 | — | Power supply terminal (+3.3V) (for D/A converter 3) (analog system) | |||

|

|

|

|

|

|

| |

54 |

| AOUTR3 | O | D/A converter 3 |

| ||

| Analog signal output for front side | ||||||

|

|

|

|

| |||

|

|

|

|

|

| ||

55 |

| AVS4 | — | Ground terminal (for D/A converter 3) (analog system) | |||

|

|

|

|

|

|

|

|

56 |

| VSS2 | — | Ground terminal (digital system) |

|

| |

|

|

|

|

|

| ||

57 |

| XRST | I | System reset signal input from the system controller (IC600) “L”: reset | |||

|

|

|

|

|

|

| |

58 |

| BFOT | O | Master clock signal output terminal | Not used (open) | ||

59 |

| SCK | I | Serial data transfer clock signal input from the system controller (IC600) and liquid crystal | |||

| display drive controller (IC800) |

|

| ||||

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

34