Power Up/Down Test Procedures

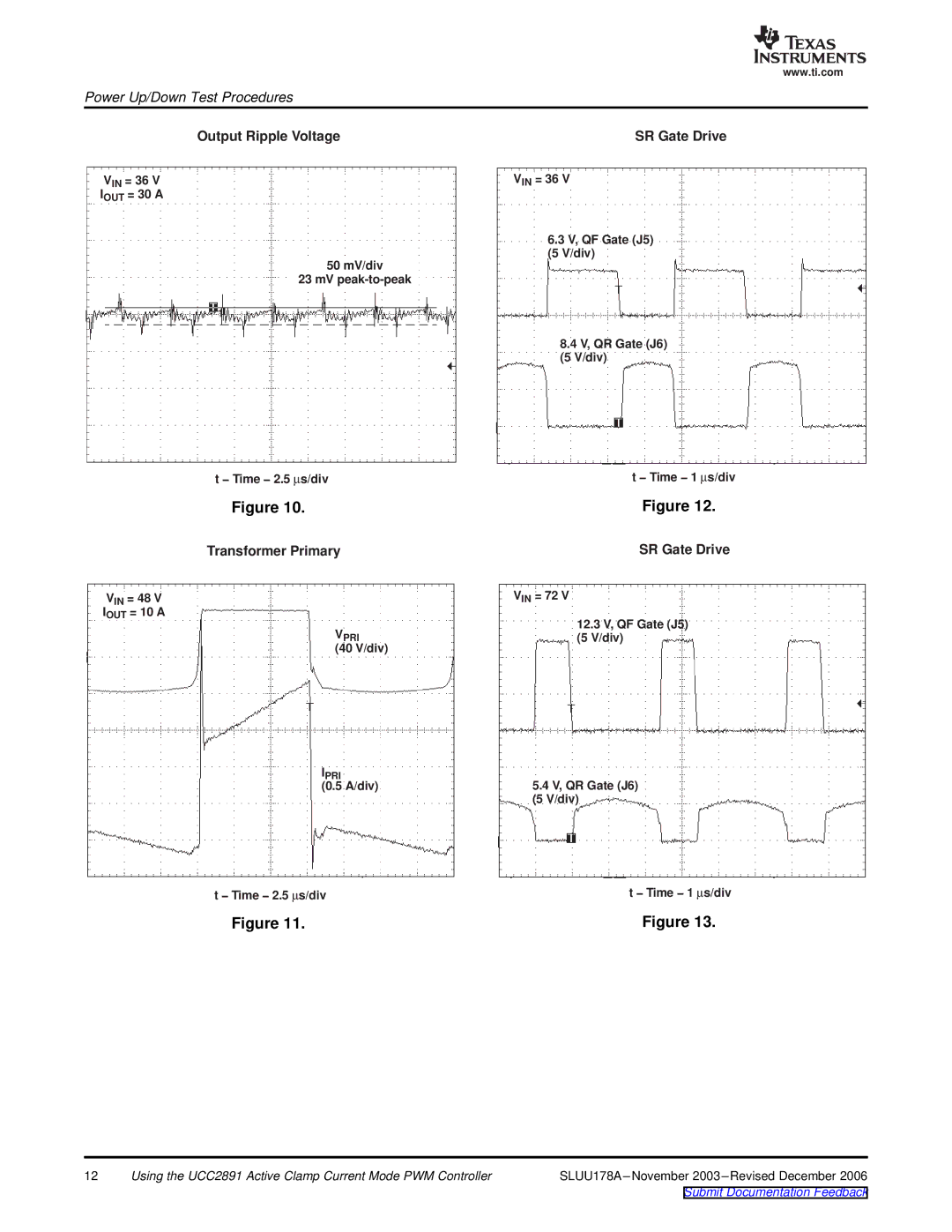

Output Ripple Voltage

VIN = 36 V

IOUT = 30 A

50 mV/div

23 mV

t − T ime − 2.5 μs/div

Figure 10.

Transformer Primary

VIN = 48 V

IOUT = 10 A

VPRI

(40 V/div)

IPRI

(0.5 A/div)

t − T ime − 2.5 μs/div

Figure 11.

12Using the UCC2891 Active Clamp Current Mode PWM Controller

www.ti.com

SR Gate Drive

VIN = 36 V

6.3V, QF Gate (J5) (5 V/div)

8.4V, QR Gate (J6) (5 V/div)

t − T ime − 1 μs/div

Figure 12.

SR Gate Drive

VIN = 72 V

12.3V, QF Gate (J5) (5 V/div)

5.4V, QR Gate (J6) (5 V/div)

t − T ime − 1 μs/div

Figure 13.

SLUU178A

Submit Documentation Feedback