R

ChipScope PLBv46 IBA (Bus Analyzer) (v1.00a)

Table 1: | IBA_PLBv46 Pin Descriptions (Continued) |

|

|

| |

|

|

|

|

|

|

Port | MU | Signal Name | Interface | I/O | Description |

|

|

|

|

|

|

P58 | MU_10 | M_abort[0: | Master | I | Master abort bus request indicator |

|

|

|

|

| |

|

|

|

|

|

|

P59 | MU_10 | PLB_rdPendPri[0:1] | Master | I | PLB pending read request priority |

|

|

|

|

|

|

P60 | MU_10 | PLB_wrPendPri[0:1] | Master | I | PLB pending write request priority |

|

|

|

|

|

|

P61 | MU_10 | PLB_rdPendReq | Master /Slave | I | PLB pending bus read request indicator |

|

|

|

|

|

|

P62 | MU_10 | PLB_wrPendReq | Master /Slave | I | PLB pending bus write request indicator |

|

|

|

|

|

|

P63 | MU_10 | PLB_reqPri[0:1] | Master /Slave | I | PLB current request priority |

|

|

|

|

|

|

|

| PLB Master Signals |

|

| |

|

|

|

|

|

|

P64 | MU_11 | M_lockErr[0: | Master | I | Master lock error indicator |

|

|

|

|

| |

|

|

|

|

|

|

P65 | MU_11 | M_rdBurst[0: | Master | I | Master read burst indicator |

|

|

|

|

| |

|

|

|

|

|

|

P66 | MU_11 | M_wrBurst[0: | Master | I | Master write burst indicator |

|

|

|

|

| |

|

|

|

|

|

|

P67 | MU_11 | M_RNW[0: | Master | I | Master read not write |

|

|

|

|

| |

|

|

|

|

|

|

P68 | MU_11 | PLB_MBusy[0: | Master | I | PLB Master slave busy indicator |

|

|

|

|

| |

|

|

|

|

|

|

P69 | MU_11 | PLB_MAddrAck[0: | Master | I | PLB Master Address acknowledge |

|

|

|

|

| |

|

|

|

|

|

|

P70 | MU_11 | PLB_MRdBTerm[0: | Master | I | PLB Master terminate read burst indicator |

|

|

|

|

| |

|

|

|

|

|

|

P71 | MU_11 | PLB_MRdDAck[0: | Master | I | PLB Master read data acknowledge |

|

|

|

|

| |

|

|

|

|

|

|

P72 | MU_11 | PLB_MRearbitrate[0: | Master | I | PLB Master bus |

|

|

|

|

| |

|

|

|

|

|

|

P73 | MU_11 | PLB_MWrBTerm[0: | Master | I | PLB Master terminate write burst indicator |

|

|

|

|

| |

|

|

|

|

|

|

P74 | MU_11 | PLB_MWrDAck[0: | Master | I | PLB Master write data acknowledge |

|

|

|

|

| |

|

|

|

|

|

|

P75 | MU_12 | M_mSize[0: | Master | I | Master data bus port width |

|

|

|

|

| |

|

|

|

|

|

|

P76 | MU_12 | M_size[0: | Master | I | Master transfer size |

|

|

|

|

|

|

|

|

|

|

|

|

P77 | MU_12 | PLB_MSSize[0: | Master | I | PLB Master slave data bus width indicator |

|

|

|

|

| |

|

|

|

|

|

|

P78 | MU_12 | M_type[0: | Master | I | Master transfer type |

|

|

|

|

|

|

|

|

|

|

|

|

P79 | MU_13 | M_BE[0: C_PLBV46_NUM_MASTERS* | Master | I | Master byte enables |

|

|

|

|

|

|

|

|

|

|

|

|

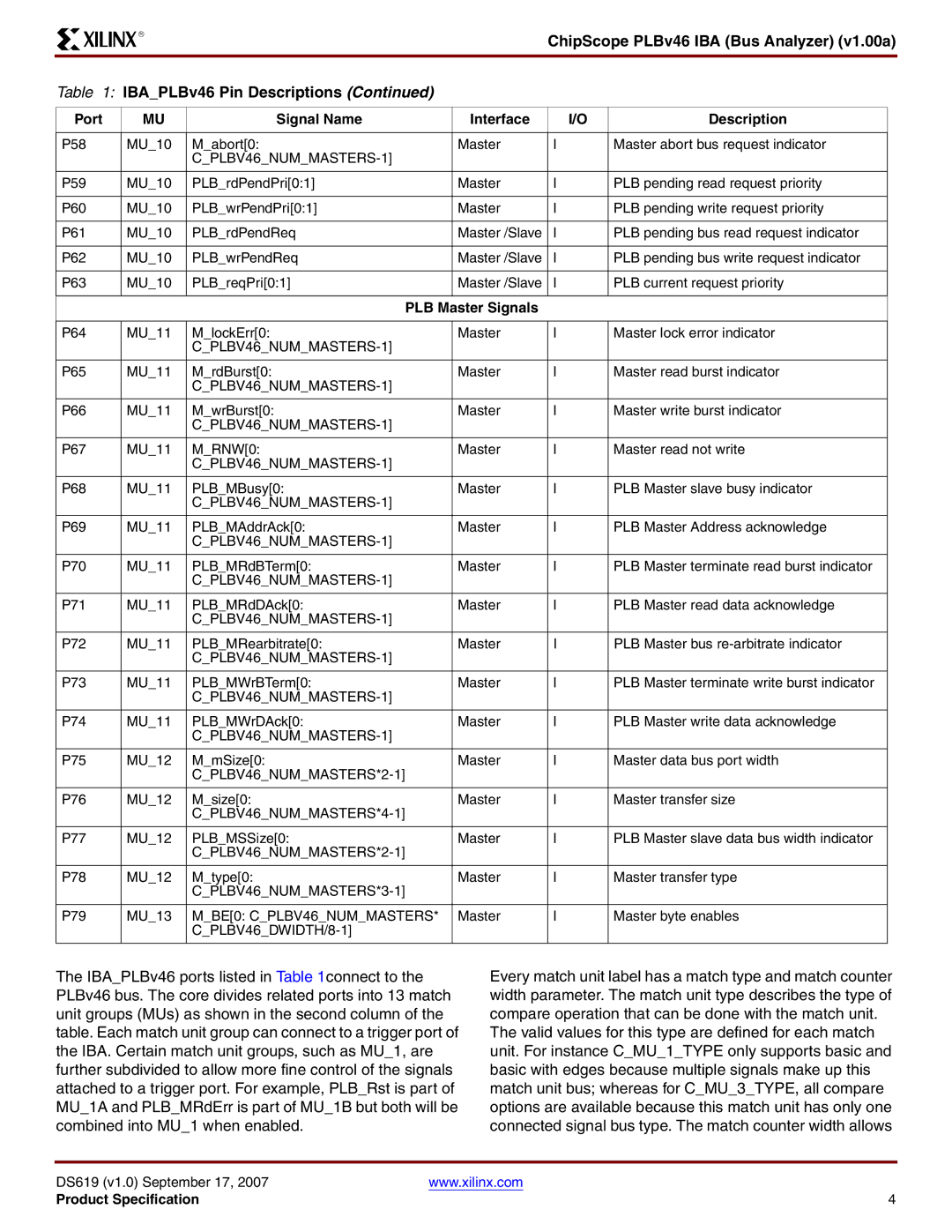

The IBA_PLBv46 ports listed in Table 1connect to the PLBv46 bus. The core divides related ports into 13 match unit groups (MUs) as shown in the second column of the table. Each match unit group can connect to a trigger port of the IBA. Certain match unit groups, such as MU_1, are further subdivided to allow more fine control of the signals attached to a trigger port. For example, PLB_Rst is part of MU_1A and PLB_MRdErr is part of MU_1B but both will be combined into MU_1 when enabled.

Every match unit label has a match type and match counter width parameter. The match unit type describes the type of compare operation that can be done with the match unit.

The valid values for this type are defined for each match unit. For instance C_MU_1_TYPE only supports basic and basic with edges because multiple signals make up this match unit bus; whereas for C_MU_3_TYPE, all compare options are available because this match unit has only one connected signal bus type. The match counter width allows

DS619 (v1.0) September 17, 2007 | www.xilinx.com |

Product Specification | 4 |