R

ChipScope PLBv46 IBA (Bus Analyzer) (v1.00a)

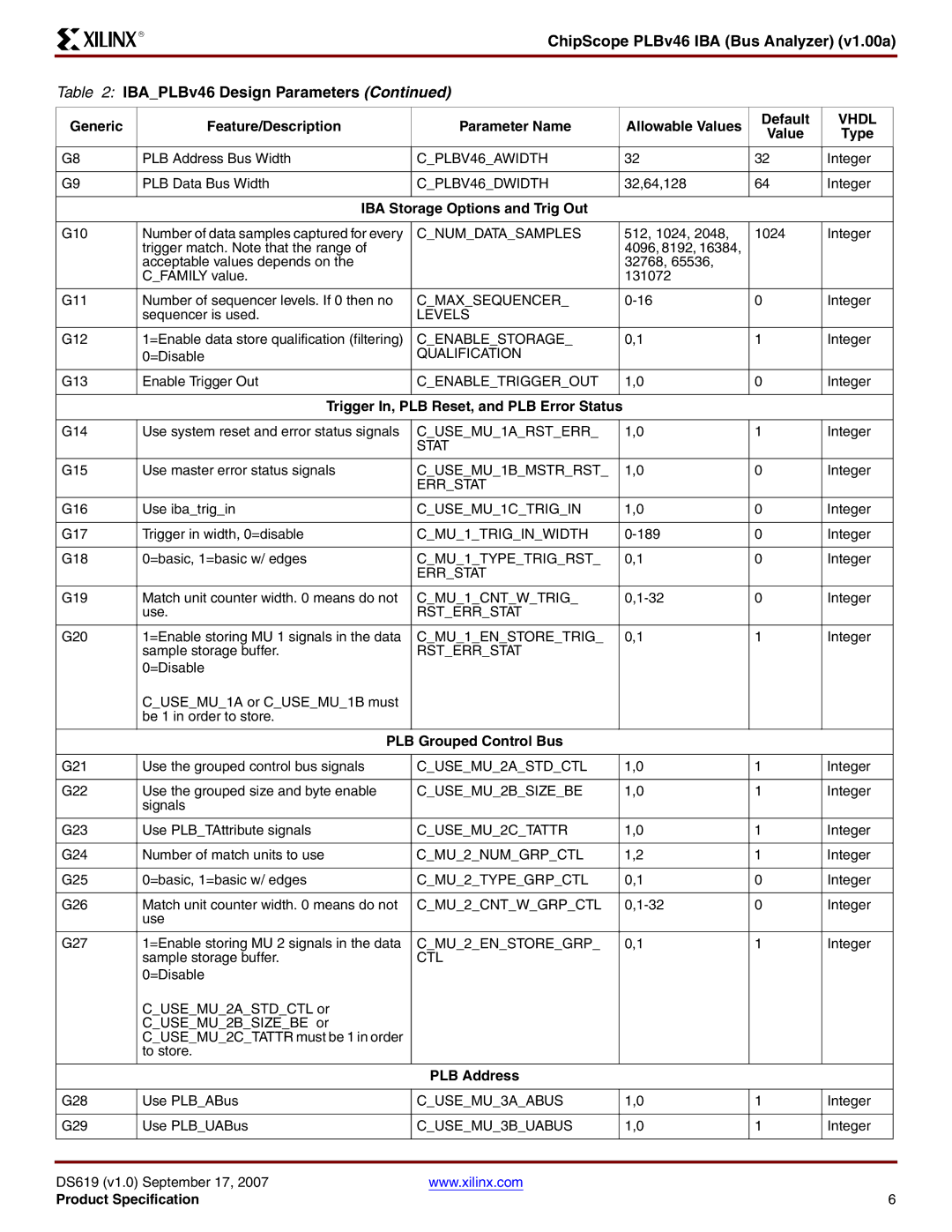

Table 2: IBA_PLBv46 Design Parameters (Continued)

Generic | Feature/Description | Parameter Name |

| Allowable Values | Default | VHDL |

|

| Value | Type |

| ||||

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

G8 | PLB Address Bus Width | C_PLBV46_AWIDTH |

| 32 | 32 | Integer |

|

|

|

|

|

|

|

|

|

G9 | PLB Data Bus Width | C_PLBV46_DWIDTH |

| 32,64,128 | 64 | Integer |

|

|

|

|

|

|

|

|

|

| IBA Storage Options and Trig Out |

|

|

|

| ||

|

|

|

|

|

|

|

|

G10 | Number of data samples captured for every | C_NUM_DATA_SAMPLES |

| 512, 1024, 2048, | 1024 | Integer |

|

| trigger match. Note that the range of |

|

| 4096, 8192, 16384, |

|

|

|

| acceptable values depends on the |

|

| 32768, 65536, |

|

|

|

| C_FAMILY value. |

|

| 131072 |

|

|

|

|

|

|

|

|

|

|

|

G11 | Number of sequencer levels. If 0 then no | C_MAX_SEQUENCER_ |

| 0 | Integer |

| |

| sequencer is used. | LEVELS |

|

|

|

|

|

|

|

|

|

|

|

|

|

G12 | 1=Enable data store qualification (filtering) | C_ENABLE_STORAGE_ |

| 0,1 | 1 | Integer |

|

| 0=Disable | QUALIFICATION |

|

|

|

|

|

|

|

|

|

|

|

|

|

G13 | Enable Trigger Out | C_ENABLE_TRIGGER_OUT |

| 1,0 | 0 | Integer |

|

|

|

|

|

|

|

|

|

| Trigger In, PLB Reset, and PLB Error Status |

|

|

|

| ||

|

|

|

|

|

|

|

|

G14 | Use system reset and error status signals | C_USE_MU_1A_RST_ERR_ |

| 1,0 | 1 | Integer |

|

|

| STAT |

|

|

|

|

|

|

|

|

|

|

|

|

|

G15 | Use master error status signals | C_USE_MU_1B_MSTR_RST_ |

| 1,0 | 0 | Integer |

|

|

| ERR_STAT |

|

|

|

|

|

|

|

|

|

|

|

|

|

G16 | Use iba_trig_in | C_USE_MU_1C_TRIG_IN |

| 1,0 | 0 | Integer |

|

|

|

|

|

|

|

|

|

G17 | Trigger in width, 0=disable | C_MU_1_TRIG_IN_WIDTH |

| 0 | Integer |

| |

|

|

|

|

|

|

|

|

G18 | 0=basic, 1=basic w/ edges | C_MU_1_TYPE_TRIG_RST_ |

| 0,1 | 0 | Integer |

|

|

| ERR_STAT |

|

|

|

|

|

|

|

|

|

|

|

|

|

G19 | Match unit counter width. 0 means do not | C_MU_1_CNT_W_TRIG_ |

| 0 | Integer |

| |

| use. | RST_ERR_STAT |

|

|

|

|

|

|

|

|

|

|

|

|

|

G20 | 1=Enable storing MU 1 signals in the data | C_MU_1_EN_STORE_TRIG_ |

| 0,1 | 1 | Integer |

|

| sample storage buffer. | RST_ERR_STAT |

|

|

|

|

|

| 0=Disable |

|

|

|

|

|

|

| C_USE_MU_1A or C_USE_MU_1B must |

|

|

|

|

|

|

| be 1 in order to store. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| PLB Grouped Control Bus |

|

|

|

| ||

|

|

|

|

|

|

|

|

G21 | Use the grouped control bus signals | C_USE_MU_2A_STD_CTL |

| 1,0 | 1 | Integer |

|

|

|

|

|

|

|

|

|

G22 | Use the grouped size and byte enable | C_USE_MU_2B_SIZE_BE |

| 1,0 | 1 | Integer |

|

| signals |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

G23 | Use PLB_TAttribute signals | C_USE_MU_2C_TATTR |

| 1,0 | 1 | Integer |

|

|

|

|

|

|

|

|

|

G24 | Number of match units to use | C_MU_2_NUM_GRP_CTL |

| 1,2 | 1 | Integer |

|

|

|

|

|

|

|

|

|

G25 | 0=basic, 1=basic w/ edges | C_MU_2_TYPE_GRP_CTL |

| 0,1 | 0 | Integer |

|

|

|

|

|

|

|

|

|

G26 | Match unit counter width. 0 means do not | C_MU_2_CNT_W_GRP_CTL |

| 0 | Integer |

| |

| use |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

G27 | 1=Enable storing MU 2 signals in the data | C_MU_2_EN_STORE_GRP_ |

| 0,1 | 1 | Integer |

|

| sample storage buffer. | CTL |

|

|

|

|

|

| 0=Disable |

|

|

|

|

|

|

| C_USE_MU_2A_STD_CTL or |

|

|

|

|

|

|

| C_USE_MU_2B_SIZE_BE or |

|

|

|

|

|

|

| C_USE_MU_2C_TATTR must be 1 in order |

|

|

|

|

|

|

| to store. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| PLB Address |

|

|

|

| |

|

|

|

|

|

|

|

|

G28 | Use PLB_ABus | C_USE_MU_3A_ABUS |

| 1,0 | 1 | Integer |

|

|

|

|

|

|

|

|

|

G29 | Use PLB_UABus | C_USE_MU_3B_UABUS |

| 1,0 | 1 | Integer |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DS619 (v1.0) September 17, 2007 | www.xilinx.com |

|

|

|

| ||

Product Specification |

|

|

|

| 6 | ||