R

ChipScope PLBv46 IBA (Bus Analyzer) (v1.00a)

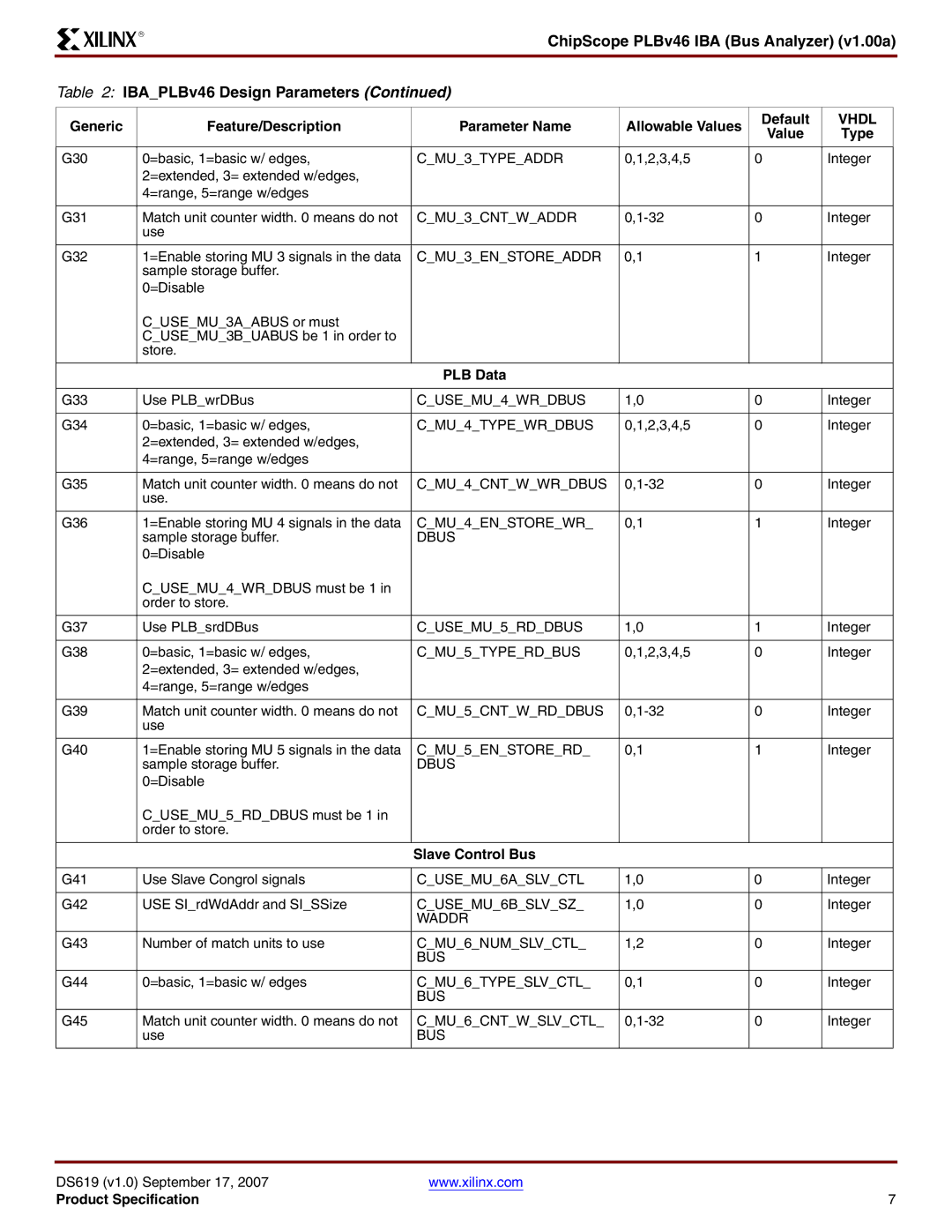

Table 2: IBA_PLBv46 Design Parameters (Continued)

Generic | Feature/Description | Parameter Name | Allowable Values | Default | VHDL | |

Value | Type | |||||

|

|

|

| |||

|

|

|

|

|

| |

G30 | 0=basic, 1=basic w/ edges, | C_MU_3_TYPE_ADDR | 0,1,2,3,4,5 | 0 | Integer | |

| 2=extended, 3= extended w/edges, |

|

|

|

| |

| 4=range, 5=range w/edges |

|

|

|

| |

|

|

|

|

|

| |

G31 | Match unit counter width. 0 means do not | C_MU_3_CNT_W_ADDR | 0 | Integer | ||

| use |

|

|

|

| |

|

|

|

|

|

| |

G32 | 1=Enable storing MU 3 signals in the data | C_MU_3_EN_STORE_ADDR | 0,1 | 1 | Integer | |

| sample storage buffer. |

|

|

|

| |

| 0=Disable |

|

|

|

| |

| C_USE_MU_3A_ABUS or must |

|

|

|

| |

| C_USE_MU_3B_UABUS be 1 in order to |

|

|

|

| |

| store. |

|

|

|

| |

|

|

|

|

|

| |

|

| PLB Data |

|

|

| |

|

|

|

|

|

| |

G33 | Use PLB_wrDBus | C_USE_MU_4_WR_DBUS | 1,0 | 0 | Integer | |

|

|

|

|

|

| |

G34 | 0=basic, 1=basic w/ edges, | C_MU_4_TYPE_WR_DBUS | 0,1,2,3,4,5 | 0 | Integer | |

| 2=extended, 3= extended w/edges, |

|

|

|

| |

| 4=range, 5=range w/edges |

|

|

|

| |

|

|

|

|

|

| |

G35 | Match unit counter width. 0 means do not | C_MU_4_CNT_W_WR_DBUS | 0 | Integer | ||

| use. |

|

|

|

| |

|

|

|

|

|

| |

G36 | 1=Enable storing MU 4 signals in the data | C_MU_4_EN_STORE_WR_ | 0,1 | 1 | Integer | |

| sample storage buffer. | DBUS |

|

|

| |

| 0=Disable |

|

|

|

| |

| C_USE_MU_4_WR_DBUS must be 1 in |

|

|

|

| |

| order to store. |

|

|

|

| |

|

|

|

|

|

| |

G37 | Use PLB_srdDBus | C_USE_MU_5_RD_DBUS | 1,0 | 1 | Integer | |

|

|

|

|

|

| |

G38 | 0=basic, 1=basic w/ edges, | C_MU_5_TYPE_RD_BUS | 0,1,2,3,4,5 | 0 | Integer | |

| 2=extended, 3= extended w/edges, |

|

|

|

| |

| 4=range, 5=range w/edges |

|

|

|

| |

|

|

|

|

|

| |

G39 | Match unit counter width. 0 means do not | C_MU_5_CNT_W_RD_DBUS | 0 | Integer | ||

| use |

|

|

|

| |

|

|

|

|

|

| |

G40 | 1=Enable storing MU 5 signals in the data | C_MU_5_EN_STORE_RD_ | 0,1 | 1 | Integer | |

| sample storage buffer. | DBUS |

|

|

| |

| 0=Disable |

|

|

|

| |

| C_USE_MU_5_RD_DBUS must be 1 in |

|

|

|

| |

| order to store. |

|

|

|

| |

|

|

|

|

|

| |

|

| Slave Control Bus |

|

|

| |

|

|

|

|

|

| |

G41 | Use Slave Congrol signals | C_USE_MU_6A_SLV_CTL | 1,0 | 0 | Integer | |

|

|

|

|

|

| |

G42 | USE SI_rdWdAddr and SI_SSize | C_USE_MU_6B_SLV_SZ_ | 1,0 | 0 | Integer | |

|

| WADDR |

|

|

| |

|

|

|

|

|

| |

G43 | Number of match units to use | C_MU_6_NUM_SLV_CTL_ | 1,2 | 0 | Integer | |

|

| BUS |

|

|

| |

|

|

|

|

|

| |

G44 | 0=basic, 1=basic w/ edges | C_MU_6_TYPE_SLV_CTL_ | 0,1 | 0 | Integer | |

|

| BUS |

|

|

| |

|

|

|

|

|

| |

G45 | Match unit counter width. 0 means do not | C_MU_6_CNT_W_SLV_CTL_ | 0 | Integer | ||

| use | BUS |

|

|

| |

|

|

|

|

|

|

DS619 (v1.0) September 17, 2007 | www.xilinx.com |

Product Specification | 7 |