HUAWEI MG323 GSM M2M Module |

|

Hardware Guide | Description of the Application Interfaces |

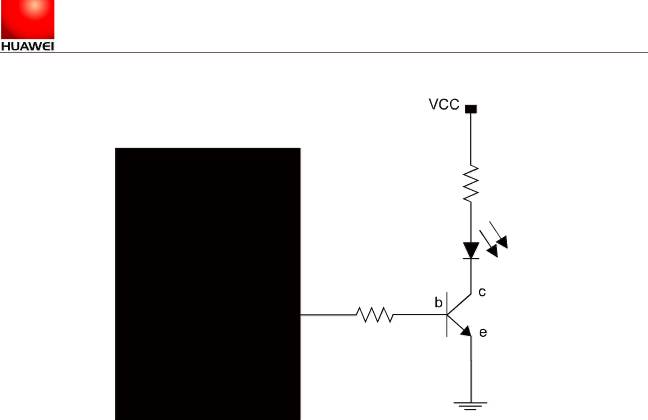

Figure 3-7 Driving circuit

3.6 UART Interface

3.6.1Overview

The MG323 module provides the UART1

Baud rate clock generated by the system clock

Direct memory access (DMA) transmission

Baud rate ranging from 9600 bit/s to 230400 bit/s (115200 bit/s by default)

Table

Table

Pin No. | Signal Name | Description | Feature | Direction |

|

|

|

|

|

29 | UART1_RD | DCE transmit | The data terminal | Data circuit- |

|

| data | equipment (DTE) | terminating |

|

|

| receives serial | equipment |

|

|

| data. | (DCE) to DTE |

|

|

|

|

|

Issue 06 | Huawei Proprietary and Confidential | 23 | |

Copyright © Huawei Technologies Co., Ltd. | |||

|

|