BIOS Setup | |

|

|

Back to Advanced Chipset Features Setup Menu:

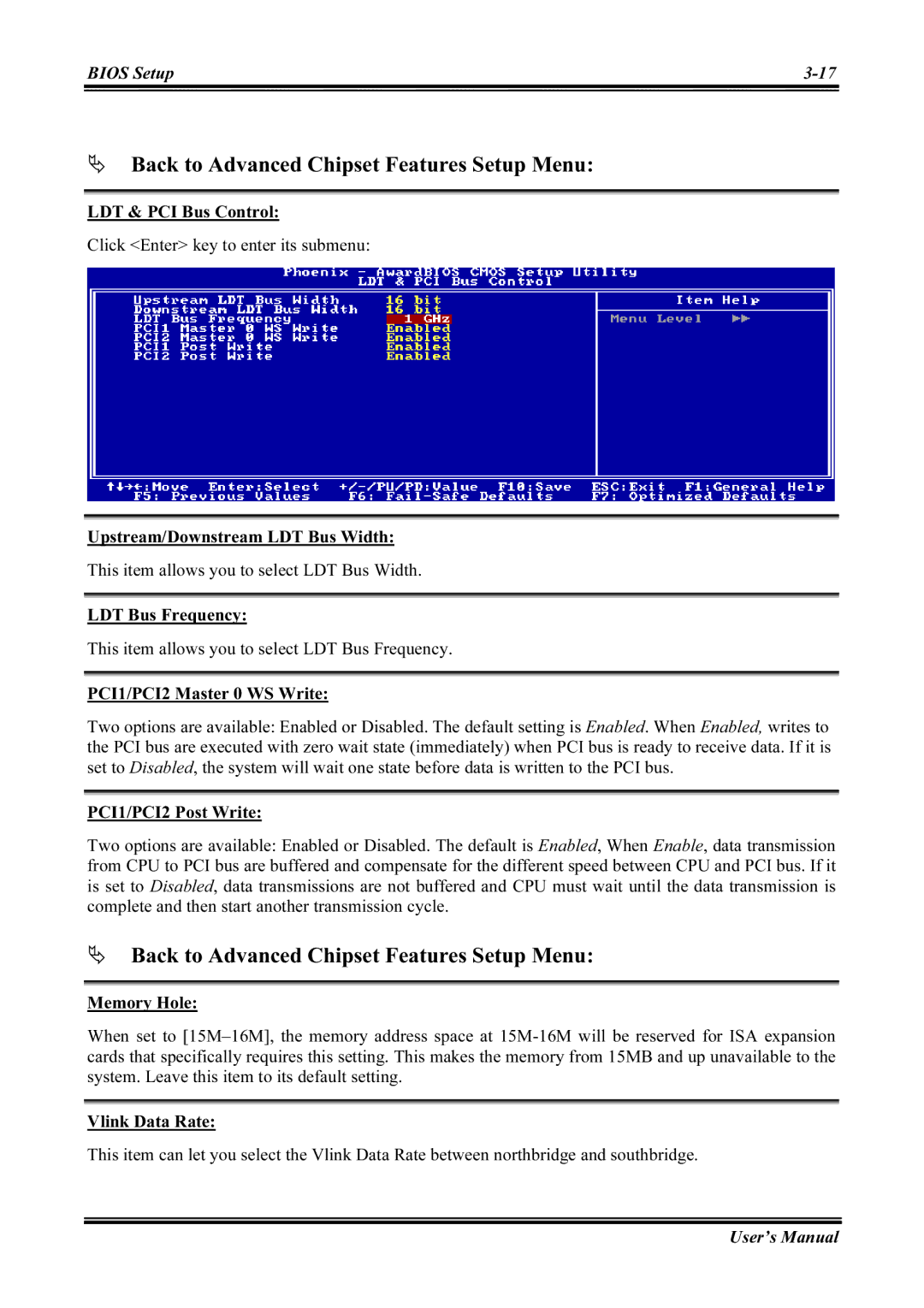

LDT & PCI Bus Control:

Click <Enter> key to enter its submenu:

Upstream/Downstream LDT Bus Width:

This item allows you to select LDT Bus Width.

LDT Bus Frequency:

This item allows you to select LDT Bus Frequency.

PCI1/PCI2 Master 0 WS Write:

Two options are available: Enabled or Disabled. The default setting is Enabled. When Enabled, writes to the PCI bus are executed with zero wait state (immediately) when PCI bus is ready to receive data. If it is set to Disabled, the system will wait one state before data is written to the PCI bus.

PCI1/PCI2 Post Write:

Two options are available: Enabled or Disabled. The default is Enabled, When Enable, data transmission from CPU to PCI bus are buffered and compensate for the different speed between CPU and PCI bus. If it is set to Disabled, data transmissions are not buffered and CPU must wait until the data transmission is complete and then start another transmission cycle.

Back to Advanced Chipset Features Setup Menu:

Memory Hole:

When set to

Vlink Data Rate:

This item can let you select the Vlink Data Rate between northbridge and southbridge.

User’s Manual