TravelMate 6492 Series Service Guide

Revision History

Copyright

Conventions

Preface

Page

Table of Contents

Machine Disassembly and Replacement

Jumper and Connector Locations 117

Page

Features

Chapter

Power Subsystem

Input devices

Audio

Communication

Environment

System Block Diagram

Mainboard Layout

Top View

Ite Nam Description

Bottom View

Cntr CN2 MDC Cntr USB

Name Description Ite

ODD Cntr

Name Description Ite

Your Acer Notebook tour

Front View

Closed Front View

Icon Description

Left View

Right View

Rear view

Base view

Indicators

Icon Function Description

HDD

Launch key Default application

Easy-Launch Buttons

Touchpad Basics

Page

Using the Keyboard

Desired Access Num Lock On Num Lock Off

Lock Keys and embedded numeric keypad

Lock Key Description

Empowering Technology on

Windows Keys

Hot Keys

Key Icon Description

Euro symbol

Special Key

US dollar sign

Acer Empowering Technology

Acer eDataSecurity Management

Chapter

Acer eLock Management

Acer ePerformance Management

Acer eRecovery Management

Acer eSettings Management

Acer ePower Management

Acer Mode

DC Mode

Create new power scheme

Chapter

Acer ePresentation Management

Acer OrbiCam

Getting to know your Acer OrbiCam

Launching the Acer OrbiCam

Changing the Acer OrbiCam settings

Using the Acer OrbiCam as webcam

Capturing photos or videos

Enabling the Acer VisageON

Page

Chapter

Using the System Utilities

Acer GridVista dual-display compatible

Launch Manager

Hardware Specifications and Configurations

Core System Description Specifications

CPU

North Intel 965GM North Bridge Package Fcbga 1299 balls

Core System Description Specifications

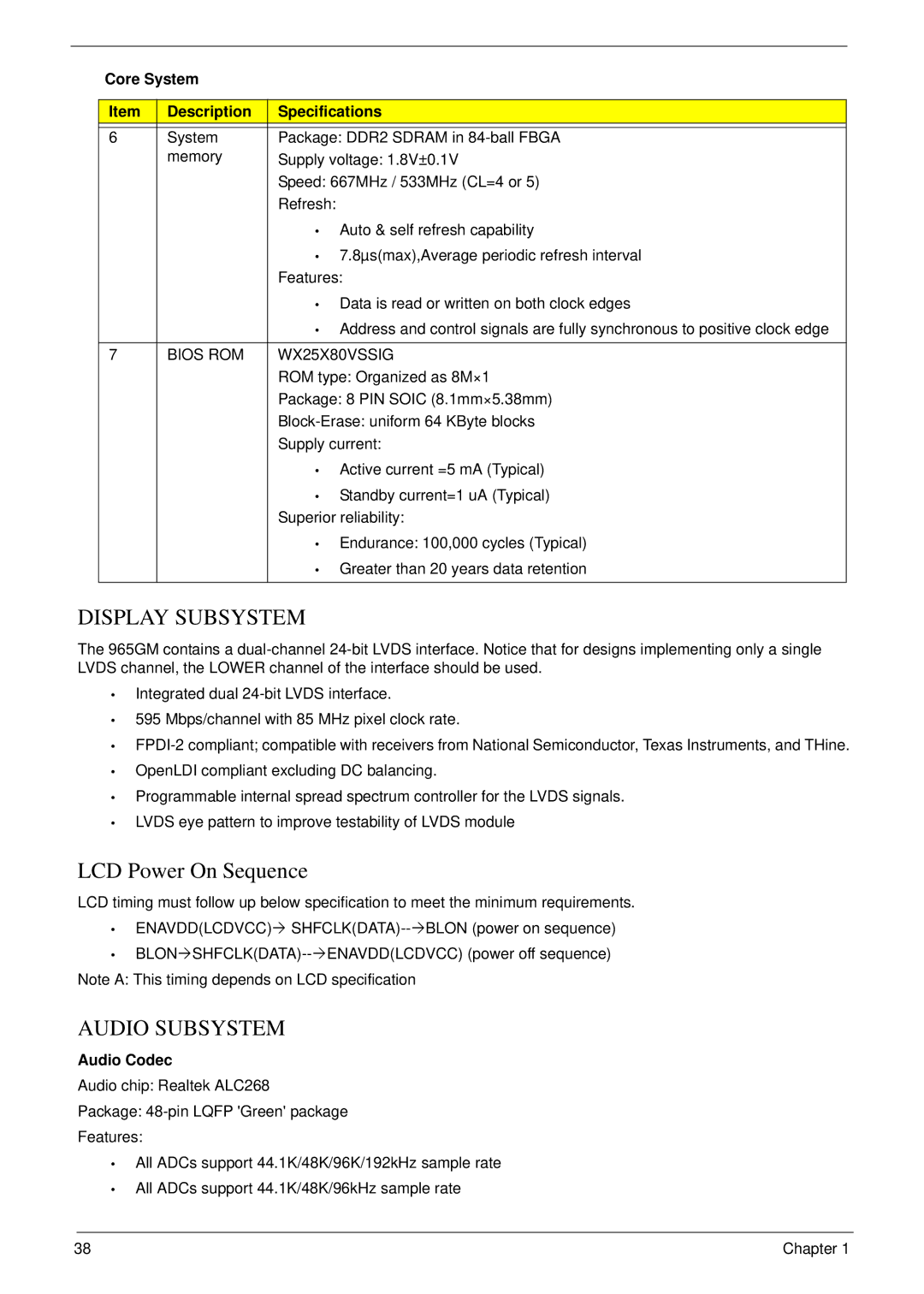

LCD Power On Sequence

Bios ROM WX25X80VSSIG

Audio Codec

PC card power controller chip for CB714

Speaker Amplifier

Audio Port

Pcmcia controller for Socket

Port

Pointing Device

Mini Card 802.11 a/g Module

Support on the System

Power Plane Active Control Device State Signal

Input Characteristics Functions Description

System LED Indicator

System LED Indicator

System Power States

Keyboard controller

Battery and Charger

Power Control Pin Description

State Output Pin

DC to DC Converter

VCC-CORE

DC-AC inverter

Parameter Min Typical Max Unit

AC adapter

Battery

Specification LiIon

Chapter

Chapter System Utilities Bios Setup Utility

Navigating the Bios Utility

Information

Parameter Description

Main

Parameter Description

F12Change Boot Device

Parameter Description Format/Option

Advanced

Parameter Description Option

ECP/SPP/EPP

Security

Password Conventions

Symbol Character Symbol Name

Clear or Set

Setting a Password

Removing a Password

Changing a Password

Chapter

Boot

USB CD/DVD ROM

Exit

Bios Flash Utility

Chapter

General Information

Before You Begin

Disassembly Procedure Flowcharts

Main Unit Disassembly Flowchart

LCM Module Disassembly Flowchart

Main Unit Disassembly Procedure

Removing the Battery Pack

Removing the CTO Cover

Removing the ODD

Removing the HDD

Removing the Btcb Screws

Removing the Memory Modules

Removing the Wireless Card

Removing the Switch Cover

Removing the Keyboard

Removing the Switch Board

Removing the Antenna Cables

Chapter

Removing the LCM Module

Removing the TouchPad

Removing the Mainboard

Page

Removing the Heatsink and Fan Module

Removing the CPU

LCM Module Disassembly Procedure

Removing the LCM Bezel

Removing the LCD Panel

Chapter

Page

LCM Module Reassembly Procedure

Replacing the LCD Panel

Page

Replacing the LCM Bezel

Main Module Reassembly Procedure

Replacing the CPU

Replacing the Heatsink and Fan Module

Replacing the Mainboard

Page

Replacing the TouchPad

Replacing the LCM Module

Replacing the Antenna Cables

Chapter

Replacing the Switch Board

Replacing the Keyboard

Chapter

Replacing the Switch Cover

Replacing the Wireless Card

Connector Number

Replacing the Memory Modules

Cable Color

Replacing the Btcb Screws

Replacing the HDD

Replacing the ODD

Replacing the Battery Pack

Replacing the CTO Cover

Troubleshooting

Symptoms Verified Go To

System Check Procedures

External Diskette Drive Check

External CD-ROM Drive Check

Keyboard or Auxiliary Input Device Check

Power System Check

Check the Power Adapter

Check the Battery Pack

Touchpad Check

Power-On Self-Test Post Error Message

Index of Error Messages

Error Codes Error Messages

Error Messages FRU/Action in Sequence

Bios ROM

Cmos Dimm

CPU ID

No beep Error Messages FRU/Action in Sequence

LCD

Post

Phoenix Bios Beep Codes

Code Beeps Post Routine Description

Setup

Code Beeps Post Routine Description

Code Beeps

Code

Index of Symptom-to-FRU Error Message

Symptom / Error Action in Sequence

PCMCIA-Related Symptoms

Pcmcia

Peripheral-Related Symptoms

Problems on Chapter 113

Intermittent Problems

Undetermined Problems

116 Chapter

Connector Locations

Name Description

Name Description CN29 IO Board Cntr D47 IR Receiver

Connector Pin Definitions

CN4 LCD I/F Connector 40-PIN PIN No Signal name

CN20 Touch PAD I/F Connector 12-PIN PIN No Signal name

CN12 Keyboard I/F Connector 25-PIN PIN No Signal name

PIN No Signal name

CN27 Cardreader Connector-TD 43-PIN PIN No Signal name

JACK501 RJ45&RJ11 Connector 14-PIN PIN No Signal name

CN7 CRT I/F Connector 15-PIN PIN No Signal name

CN501 Fan Connector 3-PIN PIN No Signal name

CN504 Board to Board Connector 30-PIN PIN No Signal name

CN513 Memory Connector 0 200-PIN PIN No Signal name

MACS#2

MABS#2

MAA9 MAA7 MAA8 MAA6

MAA5 MAA4 MAA3

MABS#1

MABS#0

MARAS#

MAWE#

CN512 Memory Connector 1 200-PIN PIN No Signal name

MBCS#2

MBBS#2

MBA9 MBA7 MBA8 MBA6

MBA5 MBA4 MBA3

CN2 S-Video 7-PIN PIN No Signal name

CN511 Multi-Bay Connector 50-PIN PIN No Signal name

CN22 USB Connector 4-PIN PIN No Signal name

CN506 RTC Battery Holder 2-PIN PIN No Signal name

CN510 HDD I/F Connector 22-PIN,SATA PIN No Signal name

CN19 PC Card Connector 68-PIN PIN No Signal name

CN28 MDC Connector 12-PIN PIN No Signal name

MC973SSDOUT GND MDC3V MC973SSYNC HAD3SSDIN1

MC973SBITCLK

CN18 Internal Microphone Connector 2-PIN PIN No Signal name

CN32/33 Internal Speaker Connector 4-PIN PIN No Signal name

CN24 MINI-PCI connector 124-PIN 1/2 PIN No Signal name

JACK4 LineIn Connector 6-PIN PIN No Signal name

JACK3 External MIC Connector 6-PIN PIN No Signal name

CN502 Battery Connector 7-PIN PIN No Signal name

+VPACK +VACK BATTERY1IN BAT1DATA BAT1CLK GND

132 Chapter

FRU Field Replaceable Unit List

TravelMate 6492 Exploded Diagrams

3G Cover Ass’y

Part Name Part Number Description

Battery Ass’y

Label

Batty Pack

BlueTooth Ass’y

MODULE, BLUETOOTH, USB

Module

Cable

Btcb Case Set Ass’y

ASSEMBLY, CASE, BOTTOM, Offline

Btcb Case Set

MN Speaker SET

BNI, Patch

CPU Ass’y

CTO Cover Set Ass’y

Display Ass’y

LCM Cable

Display Bezel Ass’y

Display Rear Ass’y

HDD Ass’y

Keyboard Ass’y

Keyb Acer MN

KEYBOARD/W ST, 88, 24P, BLACK, US-INTL

Memory Ass’y

LABEL, BLANK, REEL, 60MM, 20MM

Memory

Module Memory

Modem Ass’y

Modem

MODEM, MDC, 56K, Azalia

ODD Ass’y

Switch Cover Set Ass’y

Touchpad Bracket Set Ass’y

Tpcb CaseSet Ass’y

WAY Button

BUTTON, 4 WAY, Touch PAD, PC+ABS

Coat

Thpad Frame

Wireless Ass’y

Parts List

Category Partname Descripton Acer Part

Intel 4965AGN MOW2 Mini PCI

Cable Hotkey Board Cable

Heatsink CPU Heatsink Thermal MODULE,CPU

HDD/HARD Disk HDD 80GB 5400RPM Sata Seagate

Black Swedish ST,89,24P,BLACK,SWE

Black Traditional Chinese

CASE/COVER LCD Cover W/ Antenna FRU,LCD Bottom Case

CASE/COVER LCD Bracket Left HINGE-W

Patch Screw Screw BNI Patc

165

Appendix a

TravelMate 6492 Series

Model Country Acer Part no Description

HDD 1 GB

Appendix a

Appendix a 168

Umacf 2*512/160/BT/6L 101G16 5RNFP0.3DALES22 TM6492

Appendix a 170

AAP

Appendix a 172

USA

Appendix a 174

Test Compatible Components

Appendix B

Test Peripherals for TravelMate

Category Model/Description

Sampo PDP TV PM-42PS6

TV / LCD-TV

Epson Perfection 4870 Photo

Sanwa JY-PFFUW

Teac USB FDD FD05-PUB

ODD

MMC MMC Card 64MB

MS Card 128MB

SD Card 512MBSDSDJ-512

SM Card 128MB

Online Support Information

Appendix C

180