AN6077

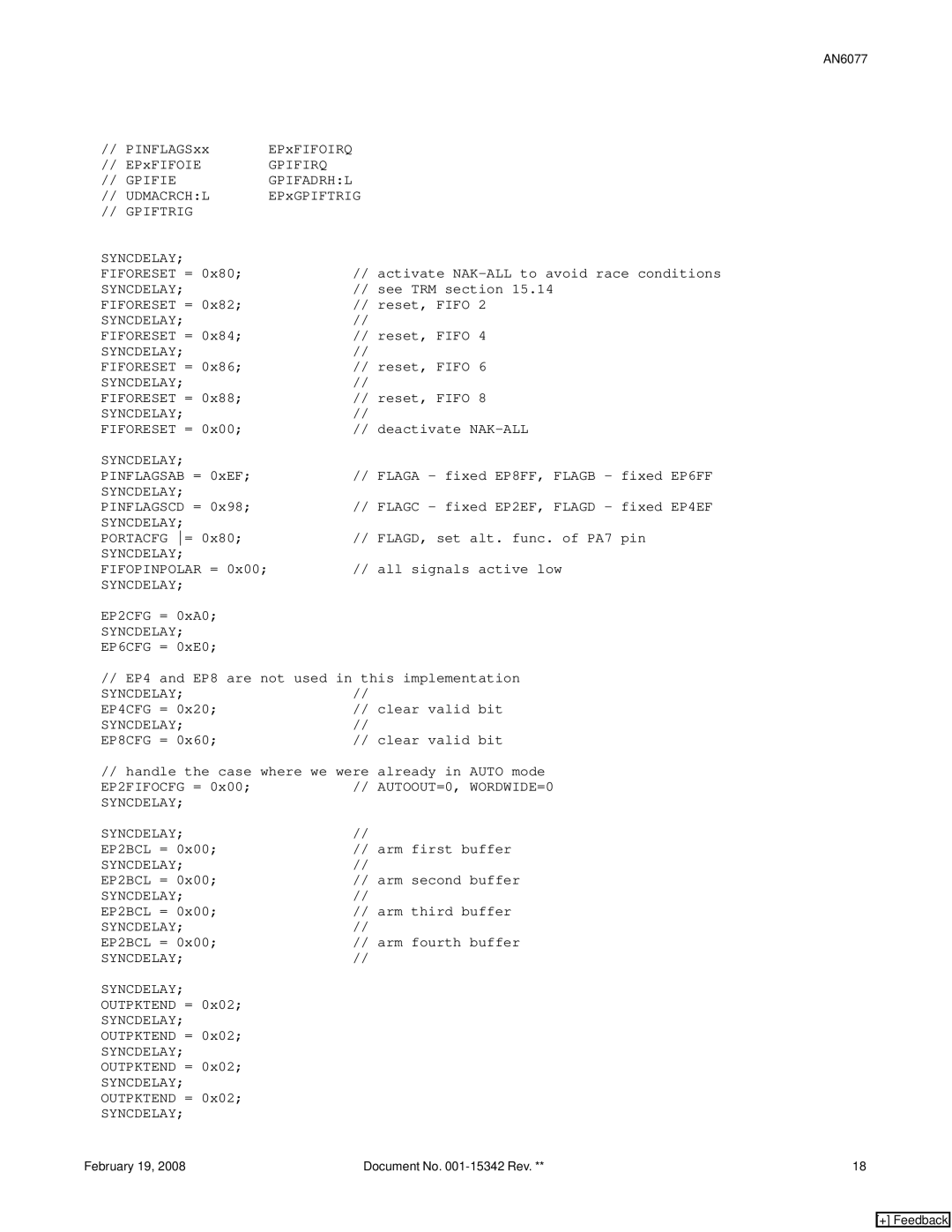

// PINFLAGSxx | EPxFIFOIRQ | |

// EPxFIFOIE | GPIFIRQ | |

// | GPIFIE | GPIFADRH:L |

// | UDMACRCH:L | EPxGPIFTRIG |

// GPIFTRIG |

|

|

|

SYNCDELAY; | // | activate |

|

FIFORESET = 0x80; |

| ||

SYNCDELAY; | // | see TRM section 15.14 |

|

FIFORESET = 0x82; | // | reset, FIFO 2 |

|

SYNCDELAY; | // | reset, FIFO 4 |

|

FIFORESET = 0x84; | // |

| |

SYNCDELAY; | // | reset, FIFO 6 |

|

FIFORESET = 0x86; | // |

| |

SYNCDELAY; | // | reset, FIFO 8 |

|

FIFORESET = 0x88; | // |

| |

SYNCDELAY; | // | deactivate |

|

FIFORESET = 0x00; | // |

| |

SYNCDELAY; | // | FLAGA - fixed EP8FF, FLAGB - fixed EP6FF |

|

PINFLAGSAB = 0xEF; |

| ||

SYNCDELAY; | // | FLAGC - fixed EP2EF, FLAGD - fixed EP4EF |

|

PINFLAGSCD = 0x98; |

| ||

SYNCDELAY; | // | FLAGD, set alt. func. of PA7 pin |

|

PORTACFG = 0x80; |

| ||

SYNCDELAY; | // | all signals active low |

|

FIFOPINPOLAR = 0x00; |

| ||

SYNCDELAY; |

|

|

|

EP2CFG = 0xA0; |

|

|

|

SYNCDELAY; |

|

|

|

EP6CFG = 0xE0; |

|

|

|

// EP4 and EP8 are not used in this implementation |

| ||

SYNCDELAY; | // | clear valid bit |

|

EP4CFG = 0x20; | // |

| |

SYNCDELAY; | // | clear valid bit |

|

EP8CFG = 0x60; | // |

| |

// handle the case where we were | already in AUTO mode |

| |

EP2FIFOCFG = 0x00; | // | AUTOOUT=0, WORDWIDE=0 |

|

SYNCDELAY; |

|

|

|

SYNCDELAY; | // | arm first buffer |

|

EP2BCL = 0x00; | // |

| |

SYNCDELAY; | // | arm second buffer |

|

EP2BCL = 0x00; | // |

| |

SYNCDELAY; | // | arm third buffer |

|

EP2BCL = 0x00; | // |

| |

SYNCDELAY; | // | arm fourth buffer |

|

EP2BCL = 0x00; | // |

| |

SYNCDELAY; | // |

|

|

SYNCDELAY; |

|

|

|

OUTPKTEND = 0x02; |

|

|

|

SYNCDELAY; |

|

|

|

OUTPKTEND = 0x02; |

|

|

|

SYNCDELAY; |

|

|

|

OUTPKTEND = 0x02; |

|

|

|

SYNCDELAY; |

|

|

|

OUTPKTEND = 0x02; |

|

|

|

SYNCDELAY; |

|

|

|

February 19, 2008 | Document No. | 18 | |