AN6077

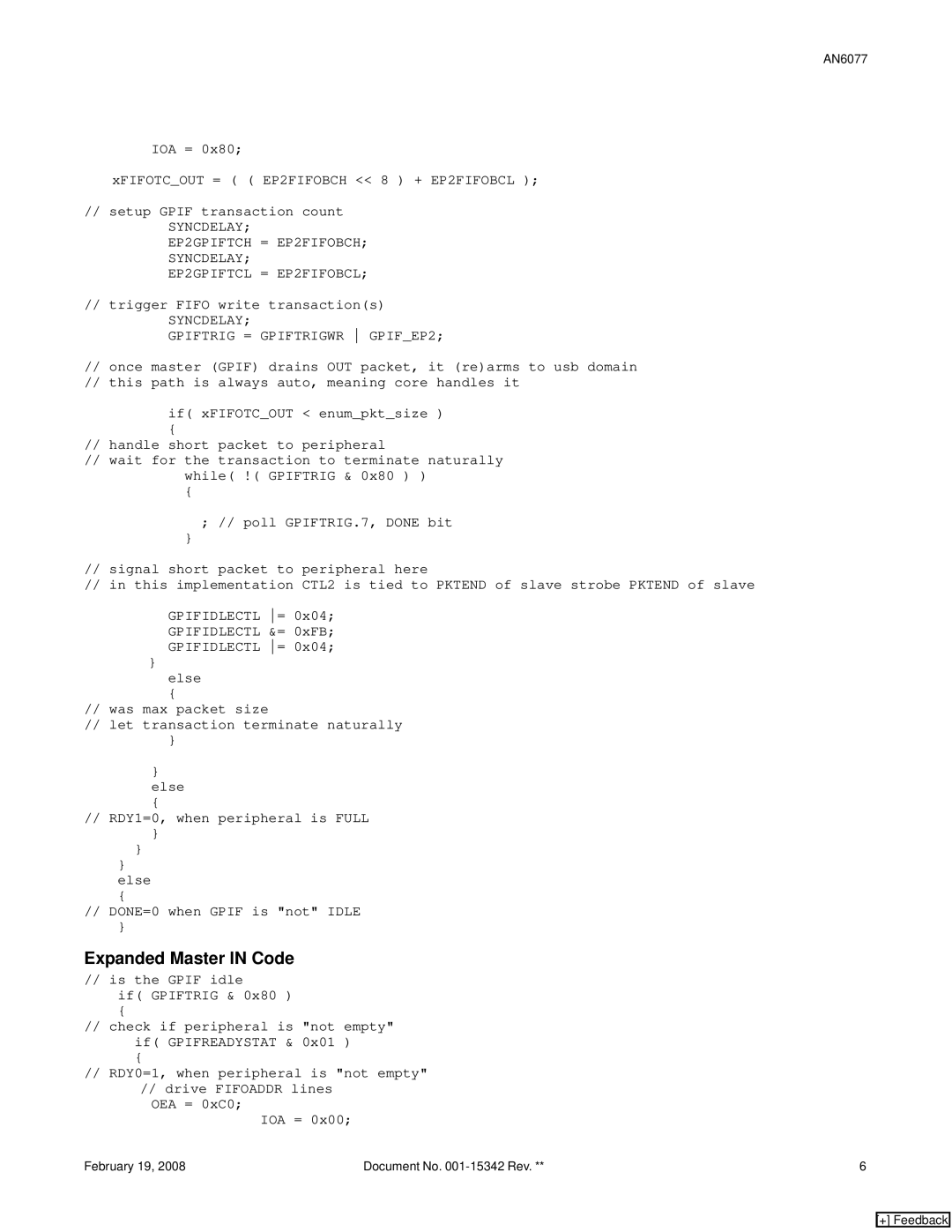

IOA = 0x80;

xFIFOTC_OUT = ( ( EP2FIFOBCH << 8 ) + EP2FIFOBCL );

//setup GPIF transaction count

SYNCDELAY;

EP2GPIFTCH = EP2FIFOBCH; SYNCDELAY;

EP2GPIFTCL = EP2FIFOBCL;

//trigger FIFO write transaction(s)

SYNCDELAY;

GPIFTRIG = GPIFTRIGWR GPIF_EP2;

//once master (GPIF) drains OUT packet, it (re)arms to usb domain

//this path is always auto, meaning core handles it

if( xFIFOTC_OUT < enum_pkt_size )

{

//handle short packet to peripheral

//wait for the transaction to terminate naturally

while( !( GPIFTRIG & 0x80 ) )

{

; // poll GPIFTRIG.7, DONE bit

}

//signal short packet to peripheral here

//in this implementation CTL2 is tied to PKTEND of slave strobe PKTEND of slave

GPIFIDLECTL = 0x04; GPIFIDLECTL &= 0xFB; GPIFIDLECTL = 0x04;

}

else

{

//was max packet size

//let transaction terminate naturally

}

}

else

{

//RDY1=0, when peripheral is FULL

}

}

}

else

{

//DONE=0 when GPIF is "not" IDLE

}

Expanded Master IN Code

// is the GPIF idle

if( GPIFTRIG & 0x80 )

{

//check if peripheral is "not empty" if( GPIFREADYSTAT & 0x01 )

{

//RDY0=1, when peripheral is "not empty"

//drive FIFOADDR lines

OEA = 0xC0;

IOA = 0x00;

February 19, 2008 | Document No. | 6 |

[+] Feedback