AN6077

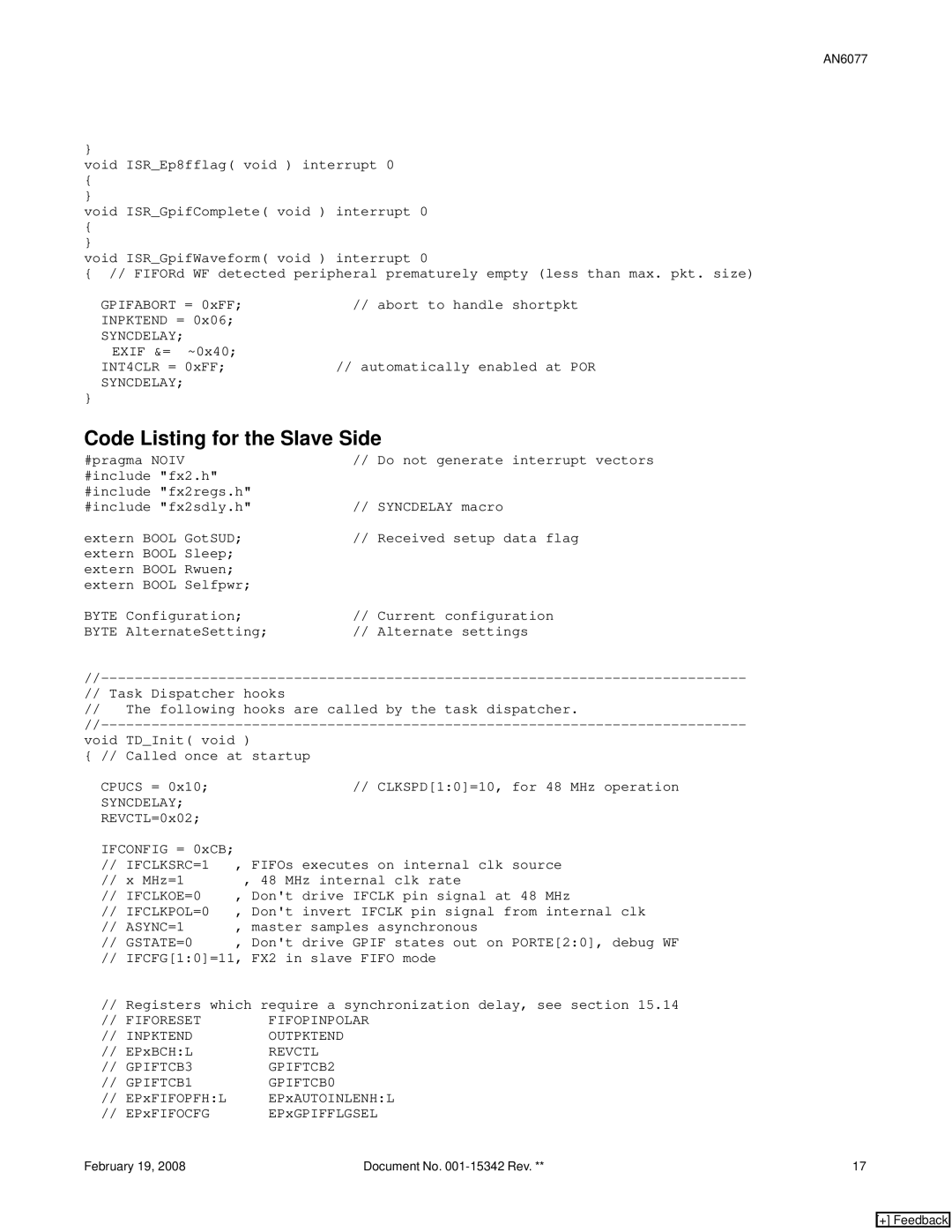

}

void ISR_Ep8fflag( void ) interrupt 0

{

}

void ISR_GpifComplete( void ) interrupt 0

{

}

void ISR_GpifWaveform( void ) interrupt 0

{// FIFORd WF detected peripheral prematurely empty (less than max. pkt. size)

GPIFABORT = 0xFF; | // abort to handle shortpkt |

INPKTEND = 0x06; |

|

SYNCDELAY; |

|

EXIF &= ~0x40; | // automatically enabled at POR |

INT4CLR = 0xFF; | |

SYNCDELAY; |

|

} |

|

Code Listing for the Slave Side

#pragma NOIV | // Do not generate interrupt vectors |

#include "fx2.h" |

|

#include "fx2regs.h" | // SYNCDELAY macro |

#include "fx2sdly.h" | |

extern BOOL GotSUD; | // Received setup data flag |

extern BOOL Sleep; |

|

extern BOOL Rwuen; |

|

extern BOOL Selfpwr; |

|

BYTE Configuration; | // Current configuration |

BYTE AlternateSetting; | // Alternate settings |

//Task Dispatcher hooks

//The following hooks are called by the task dispatcher.

TD_Init( void ) | ||

void | ||

{ // | Called once at startup | |

CPUCS = 0x10; | // CLKSPD[1:0]=10, for 48 MHz operation | |

SYNCDELAY; |

| |

REVCTL=0x02; |

| |

IFCONFIG = 0xCB; | , FIFOs executes on internal clk source | |

// | IFCLKSRC=1 | |

// | x MHz=1 | , 48 MHz internal clk rate |

// | IFCLKOE=0 | , Don't drive IFCLK pin signal at 48 MHz |

// | IFCLKPOL=0 | , Don't invert IFCLK pin signal from internal clk |

// | ASYNC=1 | , master samples asynchronous |

// | GSTATE=0 | , Don't drive GPIF states out on PORTE[2:0], debug WF |

//IFCFG[1:0]=11, FX2 in slave FIFO mode

//Registers which require a synchronization delay, see section 15.14

// FIFORESET | FIFOPINPOLAR |

|

// INPKTEND | OUTPKTEND |

|

// EPxBCH:L | REVCTL |

|

// GPIFTCB3 | GPIFTCB2 |

|

// GPIFTCB1 | GPIFTCB0 |

|

// EPxFIFOPFH:L | EPxAUTOINLENH:L |

|

// EPxFIFOCFG | EPxGPIFFLGSEL |

|

February 19, 2008 | Document No. | 17 |