AN6077

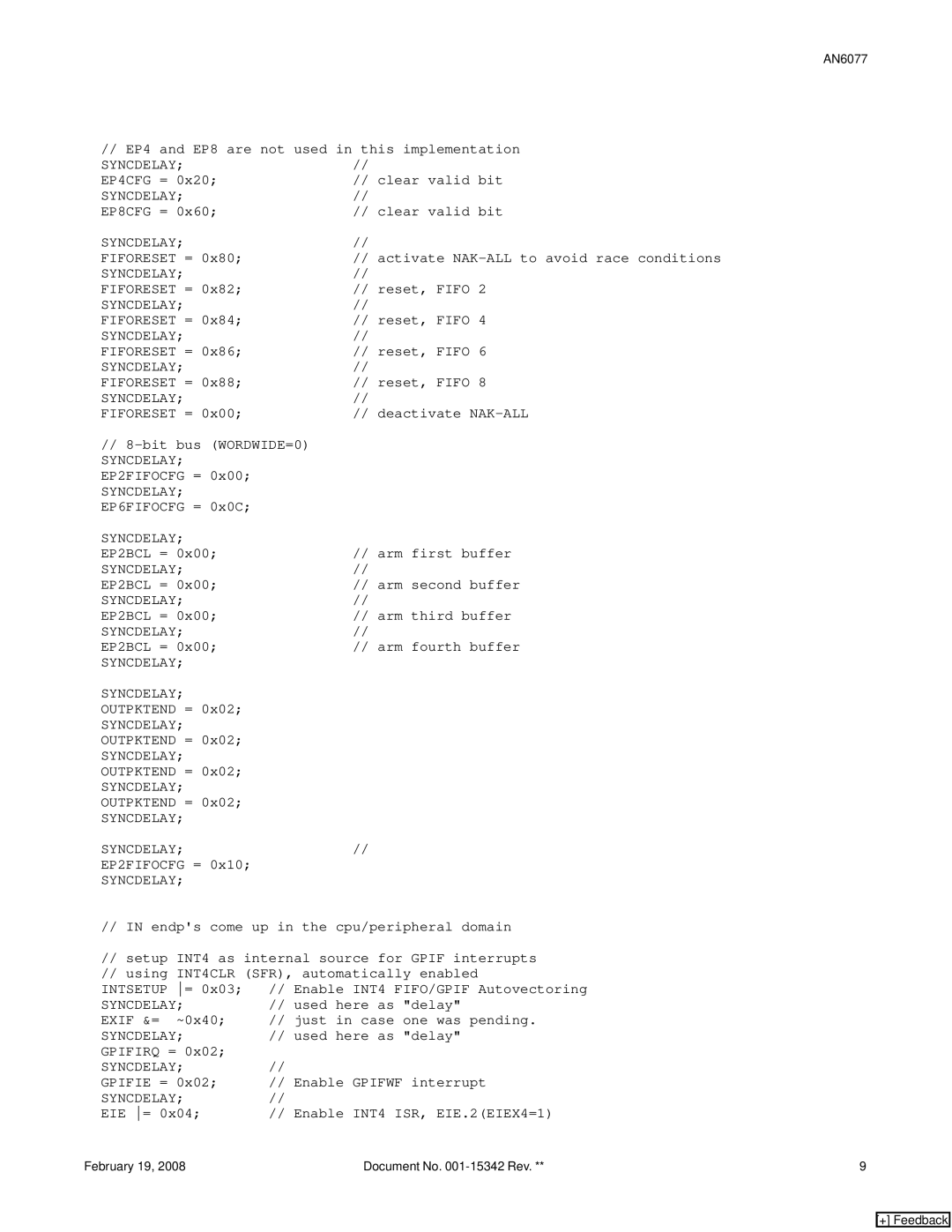

// EP4 and EP8 are not used in this implementation

SYNCDELAY; | // |

EP4CFG = 0x20; | // clear valid bit |

SYNCDELAY; | // |

EP8CFG = 0x60; | // clear valid bit |

SYNCDELAY; | // |

FIFORESET = 0x80; | // activate |

SYNCDELAY; | // |

FIFORESET = 0x82; | // reset, FIFO 2 |

SYNCDELAY; | // |

FIFORESET = 0x84; | // reset, FIFO 4 |

SYNCDELAY; | // |

FIFORESET = 0x86; | // reset, FIFO 6 |

SYNCDELAY; | // |

FIFORESET = 0x88; | // reset, FIFO 8 |

SYNCDELAY; | // |

FIFORESET = 0x00; | // deactivate |

//

SYNCDELAY; EP2FIFOCFG = 0x00;

SYNCDELAY; EP6FIFOCFG = 0x0C;

SYNCDELAY; | // arm first buffer |

EP2BCL = 0x00; | |

SYNCDELAY; | // |

EP2BCL = 0x00; | // arm second buffer |

SYNCDELAY; | // |

EP2BCL = 0x00; | // arm third buffer |

SYNCDELAY; | // |

EP2BCL = 0x00; | // arm fourth buffer |

SYNCDELAY; |

|

SYNCDELAY; |

|

OUTPKTEND = 0x02; |

|

SYNCDELAY; |

|

OUTPKTEND = 0x02; |

|

SYNCDELAY; |

|

OUTPKTEND = 0x02; |

|

SYNCDELAY; |

|

OUTPKTEND = 0x02; |

|

SYNCDELAY; |

|

SYNCDELAY; | // |

EP2FIFOCFG = 0x10; |

|

SYNCDELAY; |

|

//IN endp's come up in the cpu/peripheral domain

//setup INT4 as internal source for GPIF interrupts

//using INT4CLR (SFR), automatically enabled

INTSETUP = 0x03; // Enable INT4 FIFO/GPIF Autovectoring |

| |

SYNCDELAY; | // used here as "delay" |

|

EXIF &= ~0x40; | // just in case one was pending. |

|

SYNCDELAY; | // used here as "delay" |

|

GPIFIRQ = 0x02; | // |

|

SYNCDELAY; |

| |

GPIFIE = 0x02; | // Enable GPIFWF interrupt |

|

SYNCDELAY; | // |

|

EIE = 0x04; | // Enable INT4 ISR, EIE.2(EIEX4=1) |

|

February 19, 2008 | Document No. | 9 |

[+] Feedback