AN6077

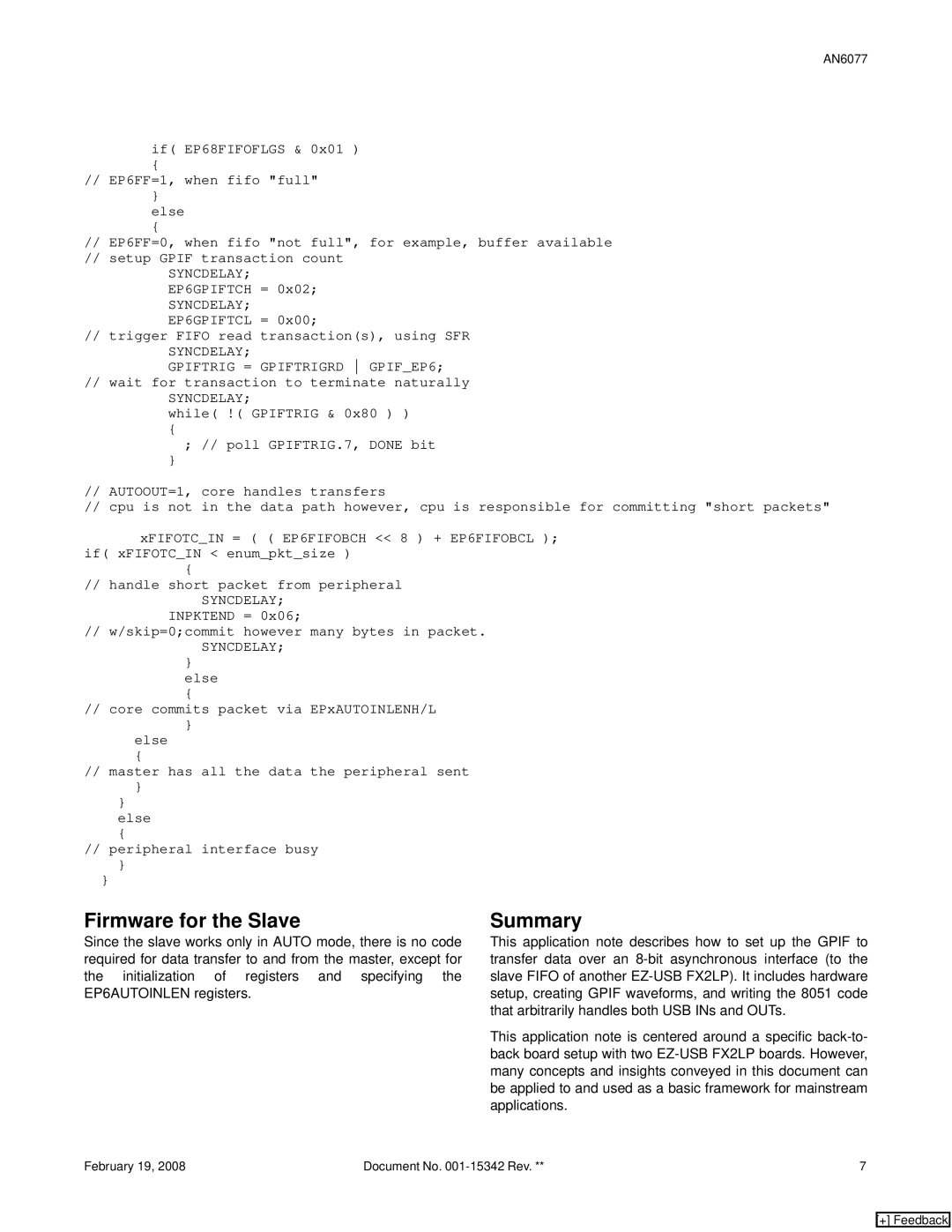

if( EP68FIFOFLGS & 0x01 )

{

//EP6FF=1, when fifo "full"

}

else

{

//EP6FF=0, when fifo "not full", for example, buffer available

//setup GPIF transaction count

SYNCDELAY;

EP6GPIFTCH = 0x02;

SYNCDELAY;

EP6GPIFTCL = 0x00;

//trigger FIFO read transaction(s), using SFR SYNCDELAY;

GPIFTRIG = GPIFTRIGRD GPIF_EP6;

//wait for transaction to terminate naturally

SYNCDELAY;

while( !( GPIFTRIG & 0x80 ) )

{

; // poll GPIFTRIG.7, DONE bit

}

//AUTOOUT=1, core handles transfers

//cpu is not in the data path however, cpu is responsible for committing "short packets"

xFIFOTC_IN = ( ( EP6FIFOBCH << 8 ) + EP6FIFOBCL ); if( xFIFOTC_IN < enum_pkt_size )

{

//handle short packet from peripheral

SYNCDELAY;

INPKTEND = 0x06;

//w/skip=0;commit however many bytes in packet.

SYNCDELAY;

}

else

{

// core commits packet via EPxAUTOINLENH/L

}

else

{

//master has all the data the peripheral sent

}

}

else

{

// peripheral interface busy

}

}

Firmware for the Slave

Since the slave works only in AUTO mode, there is no code required for data transfer to and from the master, except for the initialization of registers and specifying the EP6AUTOINLEN registers.

Summary

This application note describes how to set up the GPIF to transfer data over an

This application note is centered around a specific

February 19, 2008 | Document No. | 7 |

[+] Feedback