AN6077

}

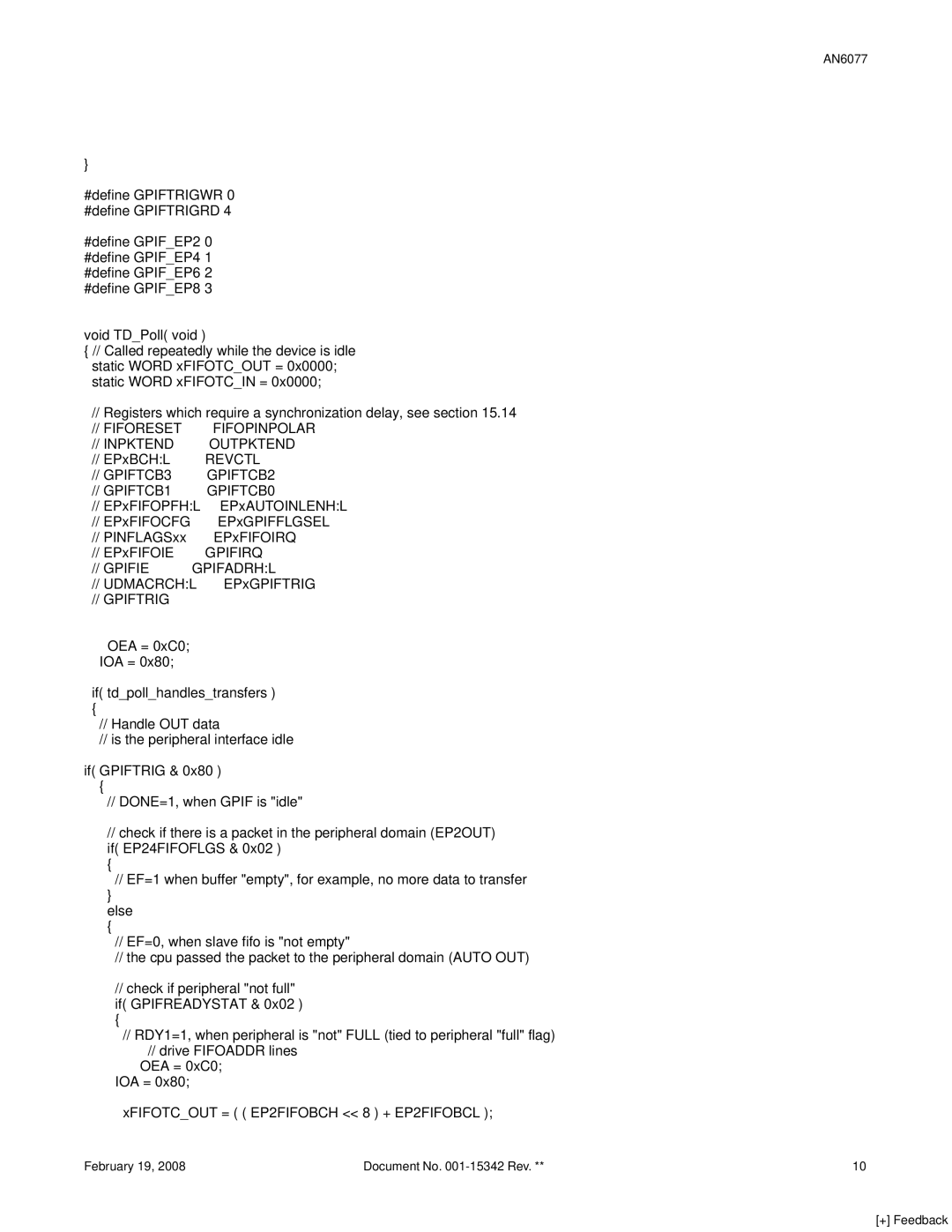

#define GPIFTRIGWR 0 #define GPIFTRIGRD 4

#define GPIF_EP2 0 #define GPIF_EP4 1 #define GPIF_EP6 2 #define GPIF_EP8 3

void TD_Poll( void )

{// Called repeatedly while the device is idle static WORD xFIFOTC_OUT = 0x0000;

static WORD xFIFOTC_IN = 0x0000;

// Registers which require a synchronization delay, see section 15.14

// FIFORESET | FIFOPINPOLAR |

// INPKTEND | OUTPKTEND |

// EPxBCH:L | REVCTL |

// GPIFTCB3 | GPIFTCB2 |

// GPIFTCB1 | GPIFTCB0 |

// EPxFIFOPFH:L | EPxAUTOINLENH:L |

// EPxFIFOCFG | EPxGPIFFLGSEL |

// PINFLAGSxx | EPxFIFOIRQ |

// EPxFIFOIE | GPIFIRQ |

// GPIFIE | GPIFADRH:L |

// UDMACRCH:L | EPxGPIFTRIG |

// GPIFTRIG |

|

OEA = 0xC0;

IOA = 0x80;

if( td_poll_handles_transfers )

{

//Handle OUT data

//is the peripheral interface idle

if( GPIFTRIG & 0x80 )

{

//DONE=1, when GPIF is "idle"

//check if there is a packet in the peripheral domain (EP2OUT) if( EP24FIFOFLGS & 0x02 )

{

//EF=1 when buffer "empty", for example, no more data to transfer

}

else

{

//EF=0, when slave fifo is "not empty"

//the cpu passed the packet to the peripheral domain (AUTO OUT)

//check if peripheral "not full"

if( GPIFREADYSTAT & 0x02 )

{

//RDY1=1, when peripheral is "not" FULL (tied to peripheral "full" flag)

//drive FIFOADDR lines

OEA = 0xC0;

IOA = 0x80;

xFIFOTC_OUT = ( ( EP2FIFOBCH << 8 ) + EP2FIFOBCL );

February 19, 2008 | Document No. | 10 |

[+] Feedback