|

|

|

|

|

|

|

| CY62148E MoBL® | |

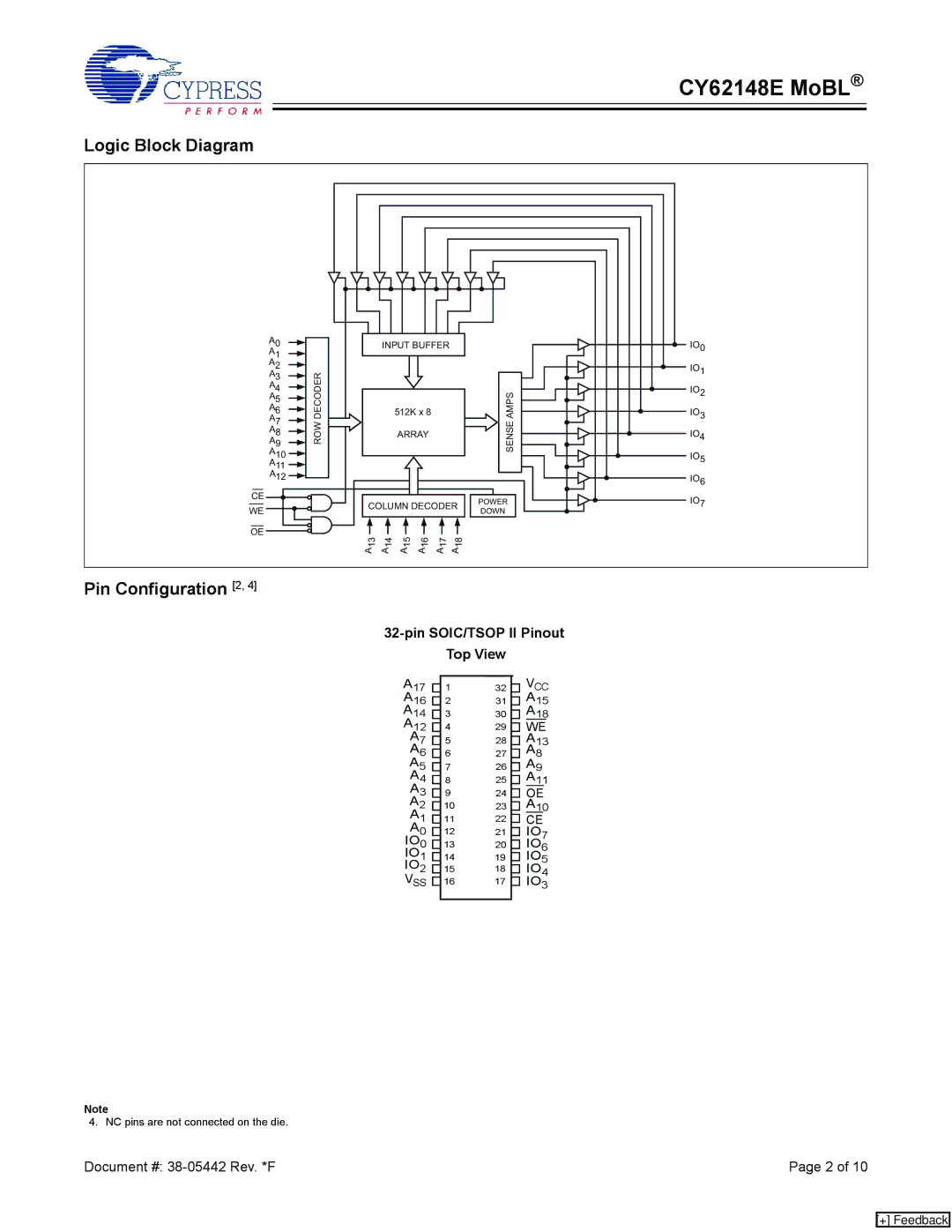

Logic Block Diagram |

|

|

|

|

|

|

|

| |

A0 |

| INPUT BUFFER |

|

| IO0 | ||||

A1 |

|

|

|

|

|

|

|

| |

A2 |

|

|

|

|

|

|

| IO1 | |

A3 | DECODER |

| 512K x 8 |

|

| AMPS | |||

A6 |

|

|

| IO3 | |||||

A4 |

|

|

|

|

|

|

| IO2 | |

A5 |

|

|

|

|

|

|

|

| |

A7 | ROW |

|

|

|

|

| SENSE |

| |

A8 |

| ARRAY |

|

| IO4 | ||||

A9 |

|

|

|

|

|

|

|

| |

A10 |

|

|

|

|

|

|

| IO5 | |

A11 |

|

|

|

|

|

|

|

| |

A12 |

|

|

|

|

|

|

| IO6 | |

CE | COLUMN DECODER | POWER | IO7 | ||||||

WE | |||||||||

|

|

|

|

|

| DOWN |

| ||

OE | 13 | 14 | 15 | 16 | 17 | 18 |

|

| |

|

|

| |||||||

| A | A | A | A | A | A |

|

| |

Pin Configuration [2, 4]

32-pin SOIC/TSOP II Pinout

Top View

A17

A16

A14

A12

A7 ![]() A6

A6 ![]() A5

A5 ![]() A4

A4 ![]() A3

A3 ![]() A2

A2 ![]() A1

A1 ![]() A0

A0 ![]() IO0

IO0 ![]() IO1

IO1 ![]() IO2

IO2 ![]()

VSS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32 |

| VCC | ||

| ||||

|

|

| A | |

31 |

|

| A15 | |

30 |

| 18 | ||

29 |

|

| WE | |

| ||||

28 |

| A13 | ||

| ||||

27 |

|

| A8 | |

| ||||

|

|

| A | |

26 |

|

| A9 | |

25 |

| 11 | ||

|

|

|

|

|

24 |

|

| OE | |

| ||||

23 |

| A10 | ||

| ||||

22 |

| CE | ||

| ||||

21IO7 IO6 IO5 IO4

IO320191817

Note

4. NC pins are not connected on the die.

Document #: | Page 2 of 10 |

[+] Feedback