CY62157EV30 MoBL®

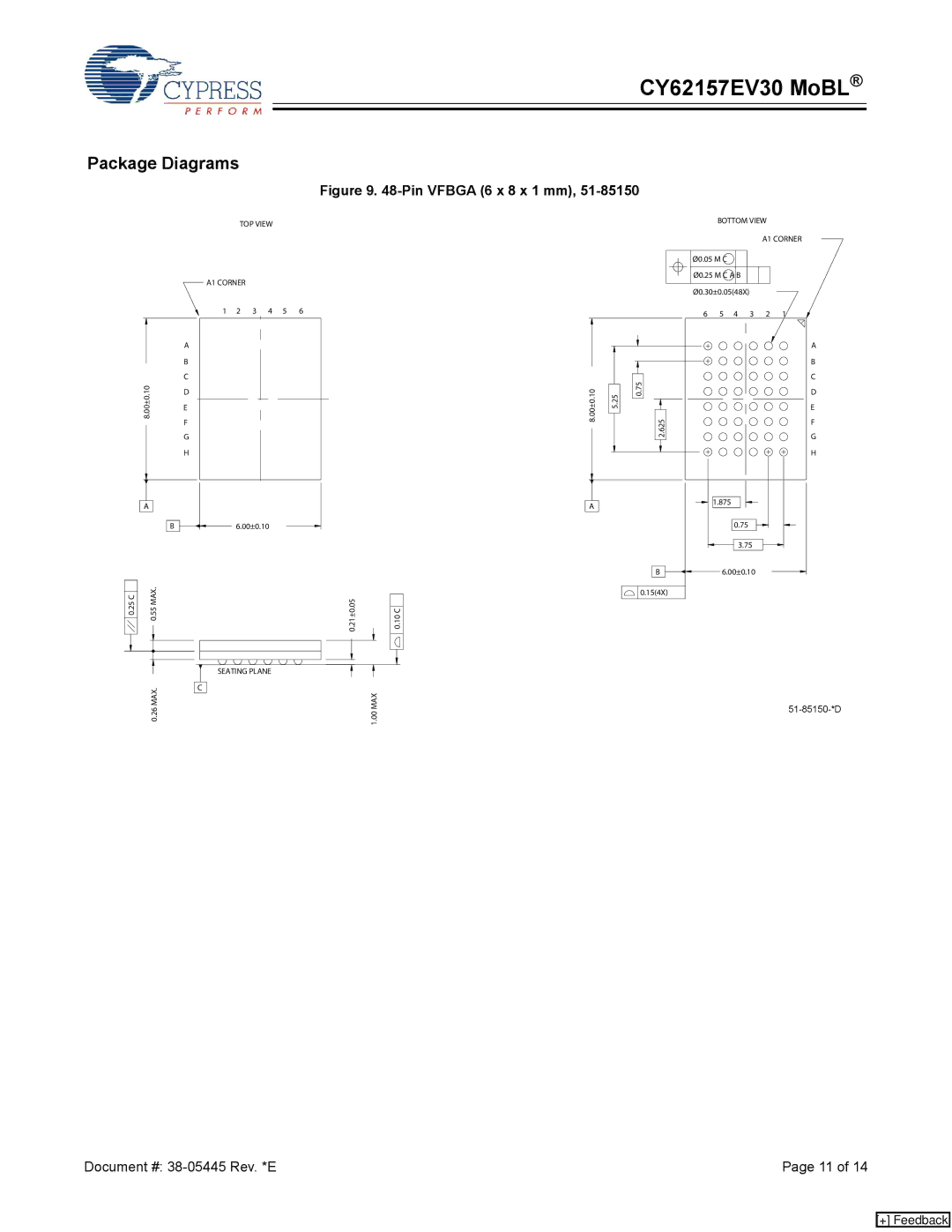

Package Diagrams

Figure 9. 48-Pin VFBGA (6 x 8 x 1 mm), 51-85150

TOP VIEW

BOTTOM VIEW

A1 CORNER

8.00±0.10

A

B

0.25 C | 0.55 MAX. |

A

B

C

D

E

F

G

H

A1 CORNER

1 2 3 4 5 6

6.00±0.10

0.21±0.05

0.10 C

8.00±0.10 | 5.25 | 0.75 | 2.625 |

A

B

0.15(4X)

Ø0.05 M C Ø0.25 M C A B Ø0.30±0.05(48X)

6 5 4 3 2 1

A

B

C

D

E

F

G

H

1.875

0.75

3.75

6.00±0.10

| SEATING PLANE |

0.26 MAX. | C |

1.00 MAX |

Document #: | Page 11 of 14 |

[+] Feedback