CY7B9911V 3.3V RoboClock+™

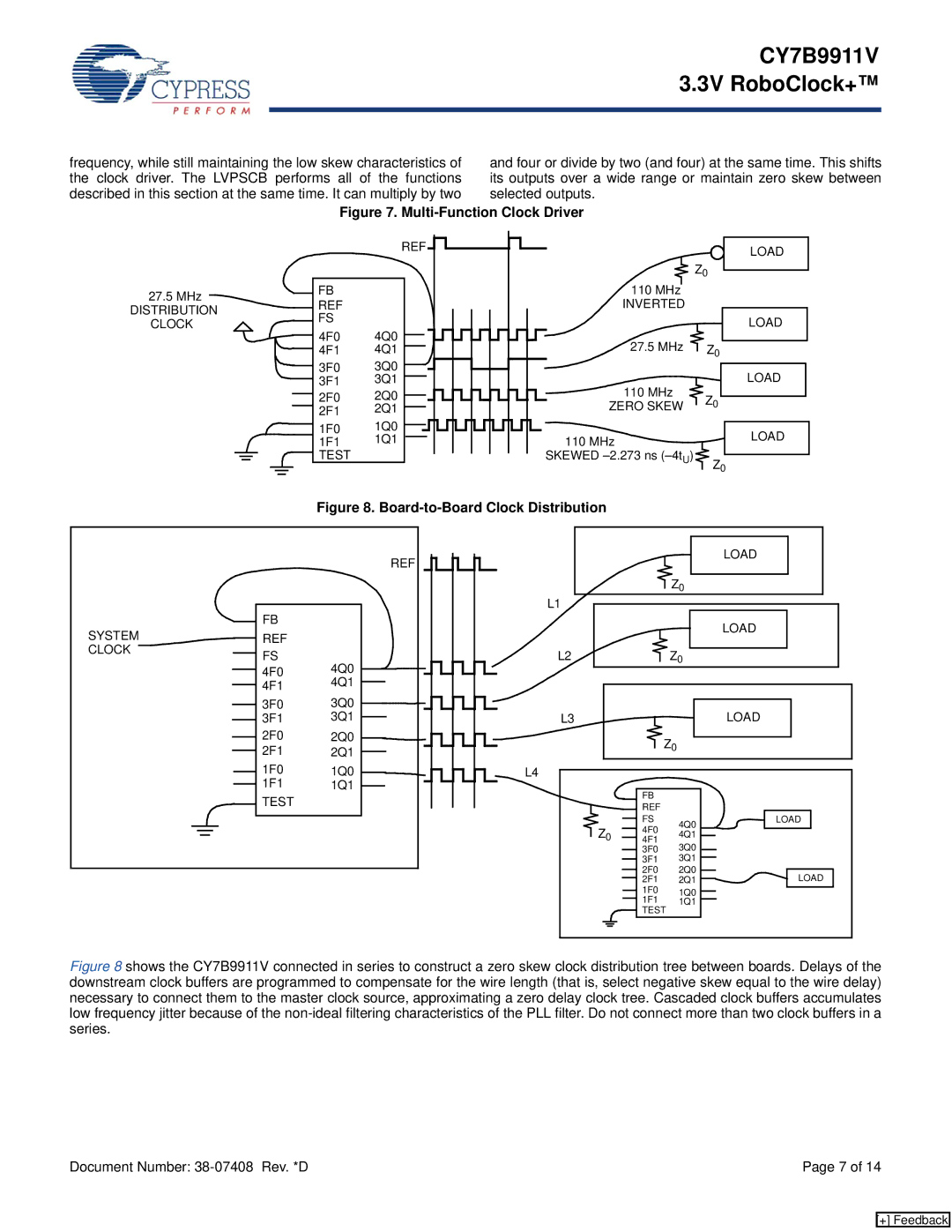

frequency, while still maintaining the low skew characteristics of the clock driver. The LVPSCB performs all of the functions described in this section at the same time. It can multiply by two

and four or divide by two (and four) at the same time. This shifts its outputs over a wide range or maintain zero skew between selected outputs.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Figure 7. |

|

|

|

|

| ||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| REF |

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Z0 | LOAD |

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 110 MHz |

|

|

| ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||

27.5 MHz |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| FB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| REF |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| INVERTED |

|

|

|

|

| |||||

DISTRIBUTION |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||||||||||||||||

|

| FS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| LOAD |

| |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

CLOCK |

| 4F0 | 4Q0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 27.5 MHz |

|

|

|

| |||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 4F1 | 4Q1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Z0 |

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 3F0 | 3Q0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 3F1 | 3Q1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| LOAD |

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 110 MHz |

|

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 2F0 | 2Q0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Z0 |

|

| |||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 2F1 | 2Q1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ZERO SKEW |

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1F0 | 1Q0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| LOAD |

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 1F1 | 1Q1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 110 MHz |

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| TEST |

|

|

|

|

|

|

|

|

|

|

|

|

|

| SKEWED |

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Z0 |

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||

|

| Figure 8. |

|

|

| |

|

|

| REF |

|

| LOAD |

|

|

|

|

|

| |

|

|

|

|

| Z0 |

|

| FB |

| L1 |

|

|

|

SYSTEM |

|

|

|

| LOAD | |

REF |

|

|

|

| ||

|

|

|

|

| ||

CLOCK | FS |

| L2 |

| Z0 |

|

| 4Q0 |

|

| |||

| 4F0 |

|

|

|

| |

| 4F1 | 4Q1 |

|

|

|

|

| 3F0 | 3Q0 |

|

|

|

|

| 3F1 | 3Q1 | L3 |

|

| LOAD |

| 2F0 | 2Q0 |

|

| Z0 |

|

| 2F1 | 2Q1 |

|

|

| |

| 1F0 | 1Q0 | L4 |

|

|

|

| 1F1 | 1Q1 |

| FB |

|

|

| TEST |

|

|

|

| |

|

|

| REF |

|

| |

|

|

|

| FS | 4Q0 | LOAD |

|

|

| Z0 | 4F0 |

| |

|

|

| 4Q1 |

| ||

|

|

| 4F1 |

| ||

|

|

|

| 3F0 | 3Q0 |

|

|

|

|

| 3F1 | 3Q1 |

|

|

|

|

| 2F0 | 2Q0 | LOAD |

|

|

|

| 2F1 | 2Q1 | |

|

|

|

| 1F0 | 1Q0 |

|

|

|

|

| 1F1 | 1Q1 |

|

|

|

|

| TEST |

| |

Figure 8 shows the CY7B9911V connected in series to construct a zero skew clock distribution tree between boards. Delays of the downstream clock buffers are programmed to compensate for the wire length (that is, select negative skew equal to the wire delay) necessary to connect them to the master clock source, approximating a zero delay clock tree. Cascaded clock buffers accumulates low frequency jitter because of the non-ideal filtering characteristics of the PLL filter. Do not connect more than two clock buffers in a series.

Document Number: | Page 7 of 14 |

[+] Feedback