CY7C1298H

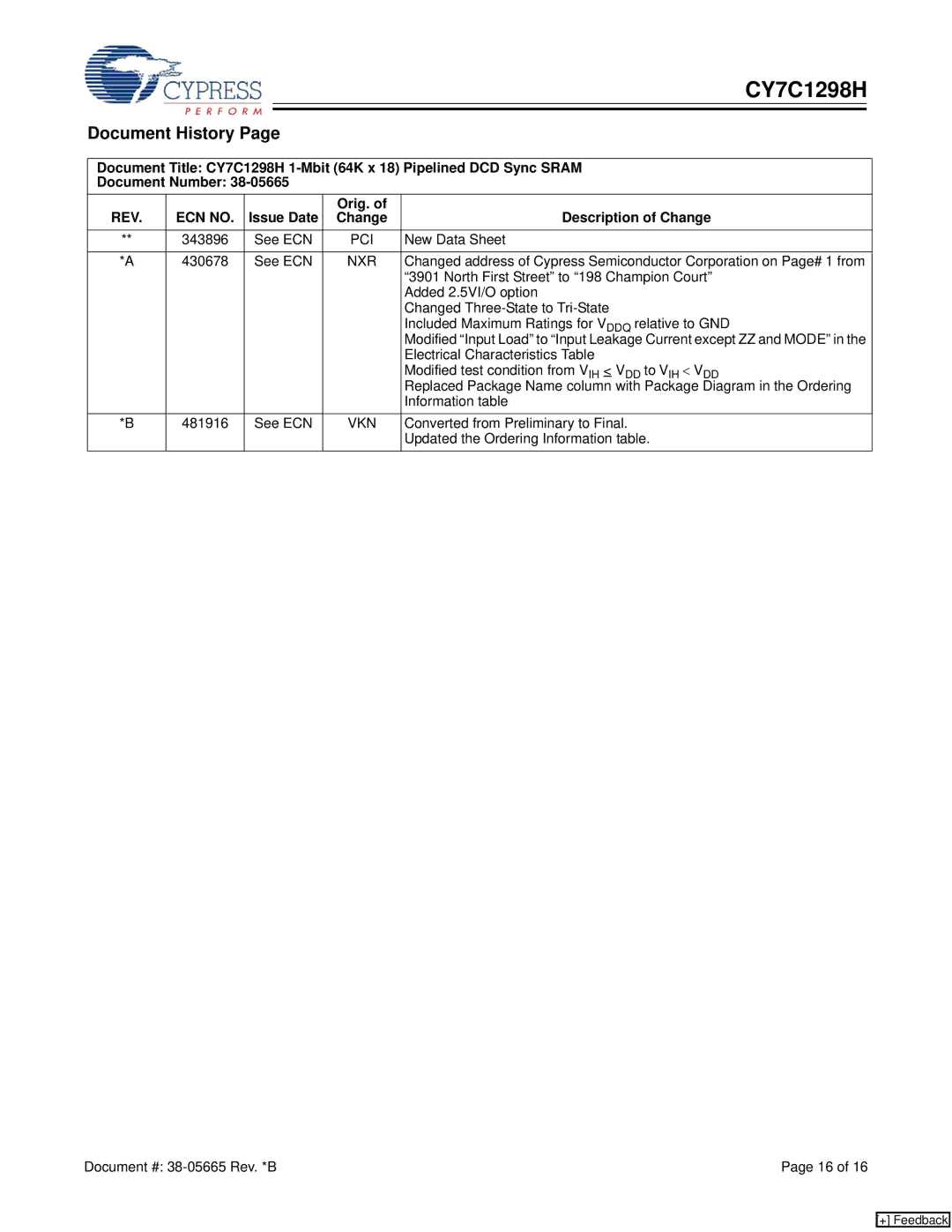

Document History Page

Document Title: CY7C1298H

Document Number:

REV. | ECN NO. | Issue Date | Orig. of | Description of Change |

Change | ||||

|

|

|

|

|

** | 343896 | See ECN | PCI | New Data Sheet |

|

|

|

|

|

*A | 430678 | See ECN | NXR | Changed address of Cypress Semiconductor Corporation on Page# 1 from |

|

|

|

| “3901 North First Street” to “198 Champion Court” |

|

|

|

| Added 2.5VI/O option |

|

|

|

| Changed |

|

|

|

| Included Maximum Ratings for VDDQ relative to GND |

|

|

|

| Modified “Input Load” to “Input Leakage Current except ZZ and MODE” in the |

|

|

|

| Electrical Characteristics Table |

|

|

|

| Modified test condition from VIH < VDD to VIH < VDD |

|

|

|

| Replaced Package Name column with Package Diagram in the Ordering |

|

|

|

| Information table |

*B | 481916 | See ECN | VKN | Converted from Preliminary to Final. |

|

|

|

| Updated the Ordering Information table. |

Document #: | Page 16 of 16 |

[+] Feedback