|

|

|

|

|

|

|

|

|

|

|

|

|

|

| CY7C1334H |

| |||

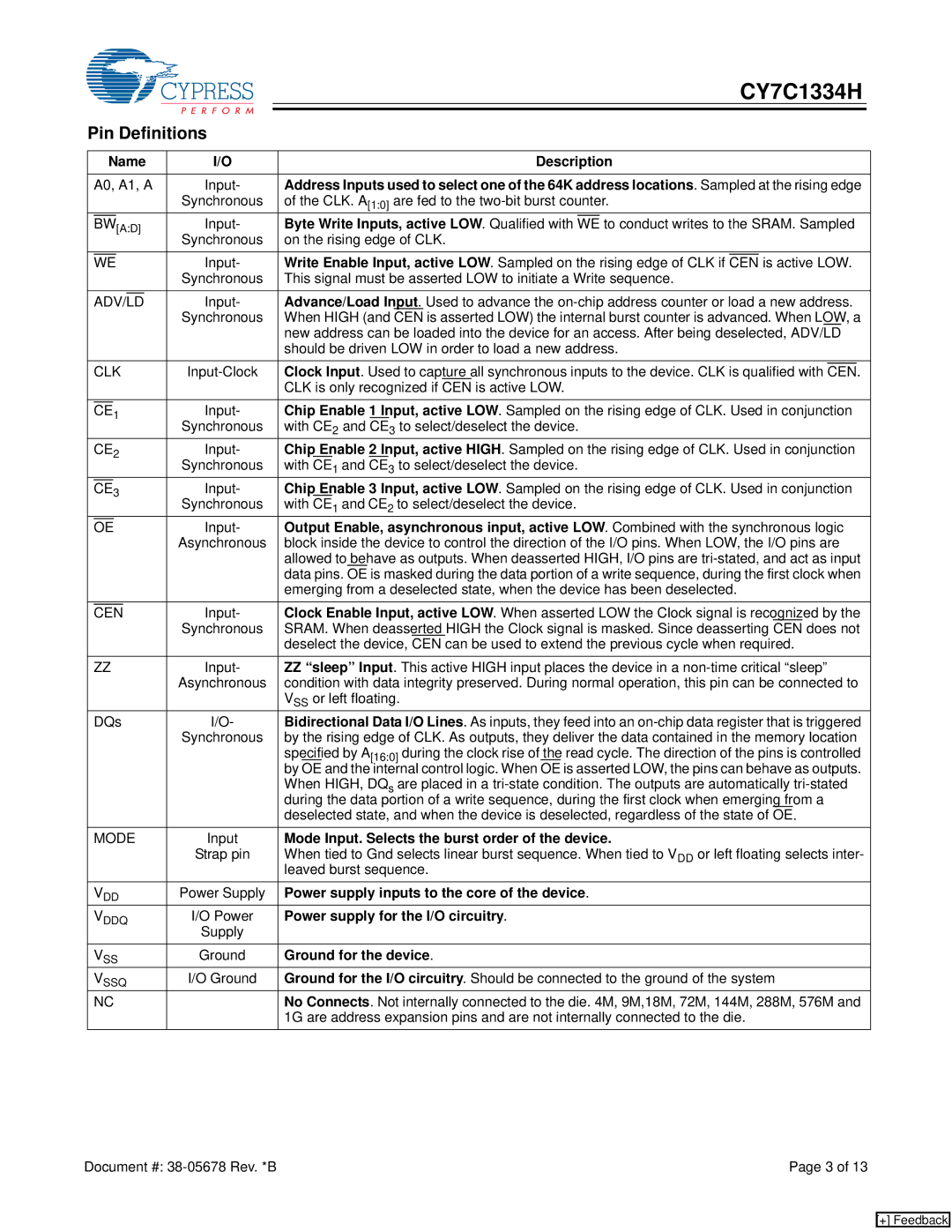

Pin Definitions |

|

|

|

|

|

|

|

|

| ||||||||||

|

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

| |||||||||||||

| Name |

| I/O |

| Description |

| |||||||||||||

|

|

|

|

|

|

| |||||||||||||

| A0, A1, A |

| Input- |

| Address Inputs used to select one of the 64K address locations. Sampled at the rising edge |

| |||||||||||||

|

|

|

|

|

|

|

|

| Synchronous |

| of the CLK. A[1:0] are fed to the |

| |||||||

|

|

|

| [A:D] |

| Input- |

| Byte Write Inputs, active LOW. Qualified with |

| to conduct writes to the SRAM. Sampled |

| ||||||||

| BW | WE |

| ||||||||||||||||

|

|

|

|

|

|

|

|

| Synchronous |

| on the rising edge of CLK. |

| |||||||

|

|

|

|

|

|

|

|

| Input- |

| Write Enable Input, active LOW. Sampled on the rising edge of CLK if |

| is active LOW. |

| |||||

| WE | CEN |

| ||||||||||||||||

|

|

|

|

|

|

|

|

| Synchronous |

| This signal must be asserted LOW to initiate a Write sequence. |

| |||||||

|

|

|

|

|

|

|

|

| Input- |

| Advance/Load Input. Used to advance the |

| |||||||

| ADV/LD |

|

|

|

| ||||||||||||||

|

|

|

|

|

|

|

|

| Synchronous |

| When HIGH (and CEN is asserted LOW) the internal burst counter is advanced. When LOW, a |

| |||||||

|

|

|

|

|

|

|

|

|

|

|

| new address can be loaded into the device for an access. After being deselected, ADV/LD |

| ||||||

|

|

|

|

|

|

|

|

|

|

|

| should be driven LOW in order to load a new address. |

| ||||||

| CLK |

|

| Clock Input. Used to capture all synchronous inputs to the device. CLK is qualified with |

|

|

| ||||||||||||

| CEN. |

| |||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| CLK is only recognized if CEN is active LOW. |

| ||||||

|

| 1 |

|

| Input- |

| Chip Enable 1 Input, active LOW. Sampled on the rising edge of CLK. Used in conjunction |

| |||||||||||

| CE |

| |||||||||||||||||

|

|

|

|

|

|

|

|

| Synchronous |

| with CE2 and CE3 to select/deselect the device. |

| |||||||

| CE2 |

| Input- |

| Chip Enable 2 Input, active HIGH. Sampled on the rising edge of CLK. Used in conjunction |

| |||||||||||||

|

|

|

|

|

|

|

|

| Synchronous |

| with CE1 and CE3 to select/deselect the device. |

| |||||||

|

| 3 |

|

| Input- |

| Chip Enable 3 Input, active LOW. Sampled on the rising edge of CLK. Used in conjunction |

| |||||||||||

| CE |

| |||||||||||||||||

|

|

|

|

|

|

|

|

| Synchronous |

| with CE1 and CE2 to select/deselect the device. |

| |||||||

|

|

|

|

|

| Input- |

| Output Enable, asynchronous input, active LOW. Combined with the synchronous logic |

| ||||||||||

| OE |

| |||||||||||||||||

|

|

|

|

|

|

|

|

| Asynchronous |

| block inside the device to control the direction of the I/O pins. When LOW, the I/O pins are |

| |||||||

|

|

|

|

|

|

|

|

|

|

|

| allowed to behave as outputs. When deasserted HIGH, I/O pins are |

| ||||||

|

|

|

|

|

|

|

|

|

|

|

| data pins. OE is masked during the data portion of a write sequence, during the first clock when |

| ||||||

|

|

|

|

|

|

|

|

|

|

|

| emerging from a deselected state, when the device has been deselected. |

| ||||||

|

|

|

|

|

|

| Input- |

| Clock Enable Input, active LOW. When asserted LOW the Clock signal is recognized by the |

| |||||||||

| CEN |

| |||||||||||||||||

|

|

|

|

|

|

|

|

| Synchronous |

| SRAM. When deasserted HIGH the Clock signal is masked. Since deasserting CEN does not |

| |||||||

|

|

|

|

|

|

|

|

|

|

|

| deselect the device, CEN can be used to extend the previous cycle when required. |

| ||||||

| ZZ |

| Input- |

| ZZ “sleep” Input. This active HIGH input places the device in a |

| |||||||||||||

|

|

|

|

|

|

|

|

| Asynchronous |

| condition with data integrity preserved. During normal operation, this pin can be connected to |

| |||||||

|

|

|

|

|

|

|

|

|

|

|

| VSS or left floating. |

| ||||||

| DQs |

| I/O- |

| Bidirectional Data I/O Lines. As inputs, they feed into an |

| |||||||||||||

|

|

|

|

|

|

|

|

| Synchronous |

| by the rising edge of CLK. As outputs, they deliver the data contained in the memory location |

| |||||||

|

|

|

|

|

|

|

|

|

|

|

| specified by A[16:0] during the clock rise of the read cycle. The direction of the pins is controlled |

| ||||||

|

|

|

|

|

|

|

|

|

|

|

| by OE and the internal control logic. When OE is asserted LOW, the pins can behave as outputs. |

| ||||||

|

|

|

|

|

|

|

|

|

|

|

| When HIGH, DQs are placed in a |

| ||||||

|

|

|

|

|

|

|

|

|

|

|

| during the data portion of a write sequence, during the first clock when emerging from a |

| ||||||

|

|

|

|

|

|

|

|

|

|

|

| deselected state, and when the device is deselected, regardless of the state of OE. |

| ||||||

| MODE |

| Input |

| Mode Input. Selects the burst order of the device. |

| |||||||||||||

|

|

|

|

|

|

|

|

| Strap pin |

| When tied to Gnd selects linear burst sequence. When tied to VDD or left floating selects inter- |

| |||||||

|

|

|

|

|

|

|

|

|

|

|

| leaved burst sequence. |

| ||||||

| VDD |

| Power Supply |

| Power supply inputs to the core of the device. |

| |||||||||||||

| VDDQ |

| I/O Power |

| Power supply for the I/O circuitry. |

| |||||||||||||

|

|

|

|

|

|

|

|

| Supply |

|

|

|

|

|

|

|

|

| |

| VSS |

| Ground |

| Ground for the device. |

| |||||||||||||

| VSSQ |

| I/O Ground |

| Ground for the I/O circuitry. Should be connected to the ground of the system |

| |||||||||||||

| NC |

|

|

|

| No Connects. Not internally connected to the die. 4M, 9M,18M, 72M, 144M, 288M, 576M and |

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| 1G are address expansion pins and are not internally connected to the die. |

| ||||||

Document #: | Page 3 of 13 |

[+] Feedback