CY7C1541V18, CY7C1556V18

CY7C1543V18, CY7C1545V18

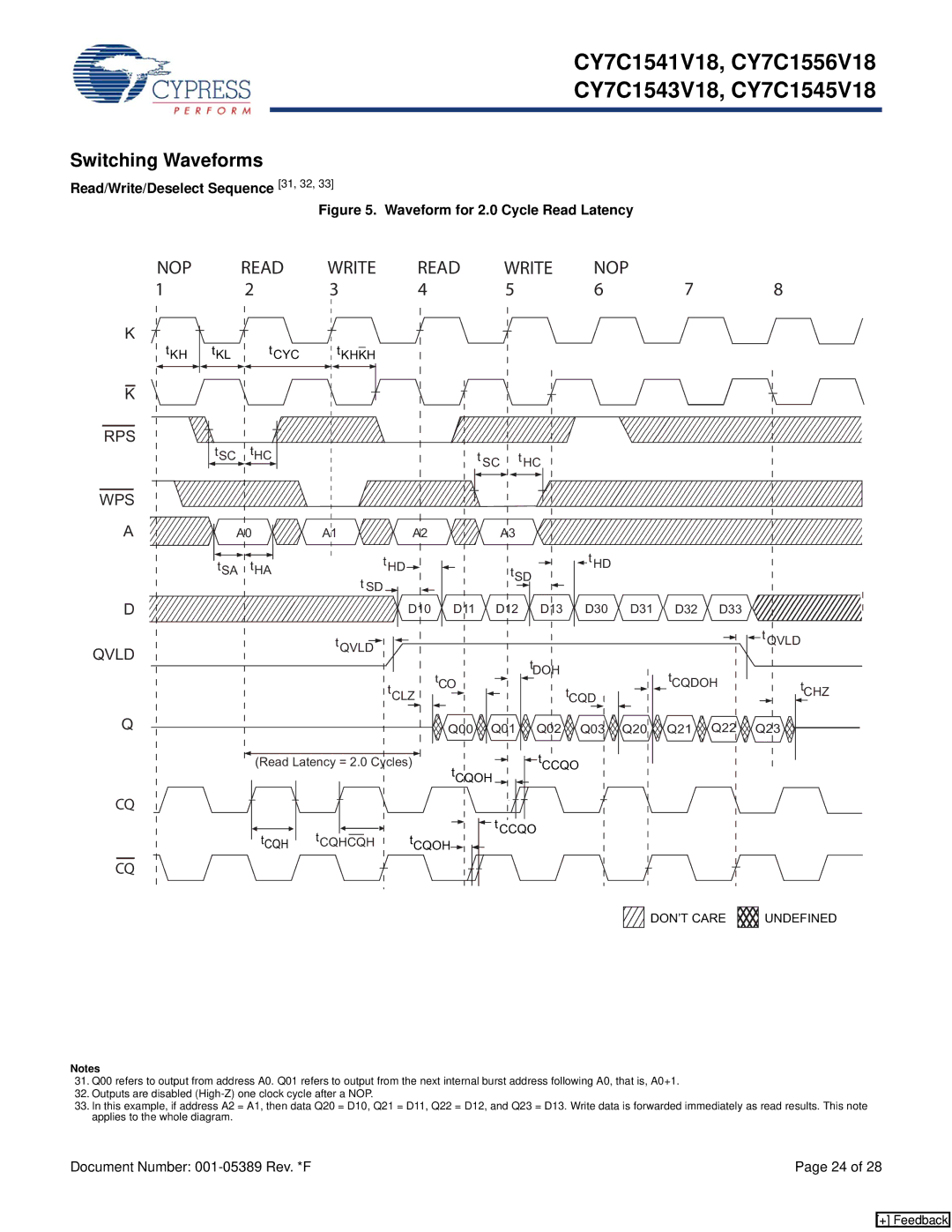

Switching Waveforms

Read/Write/Deselect Sequence [31, 32, 33]

Figure 5. Waveform for 2.0 Cycle Read Latency

NOP | READ | WRITE | READ | WRITE | NOP |

|

|

1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

K

tKH

K

tKL tCYC tKHKH

RPS |

|

tSC tHC | t SC tHC |

WPS

A

D

QVLD

A0 | A1 | A2 |

| A3 |

|

|

|

|

|

tSA tHA | t | HD |

| tSD | tHD |

|

|

| |

t SD |

|

|

|

|

| ||||

|

|

|

|

|

|

|

|

| |

|

| D10 | D11 | D12 | D13 | D30 | D31 | D32 | D33 |

| tQVLD |

|

|

|

|

|

|

|

|

|

|

| tCO |

| tDOH |

|

| tCQDOH |

|

|

| tCLZ |

|

| tCQD |

|

| ||

|

|

|

|

|

|

|

| ||

![]() tQVLD

tQVLD

tCHZ

Q

CQ

CQ

![]()

![]() Q00

Q00![]() Q01

Q01![]() Q02

Q02 ![]() Q03

Q03![]() Q20

Q20 ![]() Q21

Q21 ![]() Q22

Q22![]() Q23

Q23![]()

(Read Latency = 2.0 Cycles) |

| t | |

tCQOH | CCQO | ||

|

|

| |

tCQH tCQHCQH |

| t | CCQO |

tCQOH |

| ||

|

| ||

DON’T CARE

UNDEFINED

Notes

31.Q00 refers to output from address A0. Q01 refers to output from the next internal burst address following A0, that is, A0+1.

32.Outputs are disabled

33.In this example, if address A2 = A1, then data Q20 = D10, Q21 = D11, Q22 = D12, and Q23 = D13. Write data is forwarded immediately as read results. This note applies to the whole diagram.

Document Number: | Page 24 of 28 |

[+] Feedback