CY7C1566V18, CY7C1577V18 CY7C1568V18, CY7C1570V18

Echo Clocks

Echo clocks are provided on the

Valid Data Indicator (QVLD)

QVLD is provided on the

DLL

These chips use a Delay Lock Loop (DLL) that is designed to function between 120 MHz and the specified maximum clock frequency. The DLL may be disabled by applying ground to the DOFF pin. When the DLL is turned off, the device behaves in

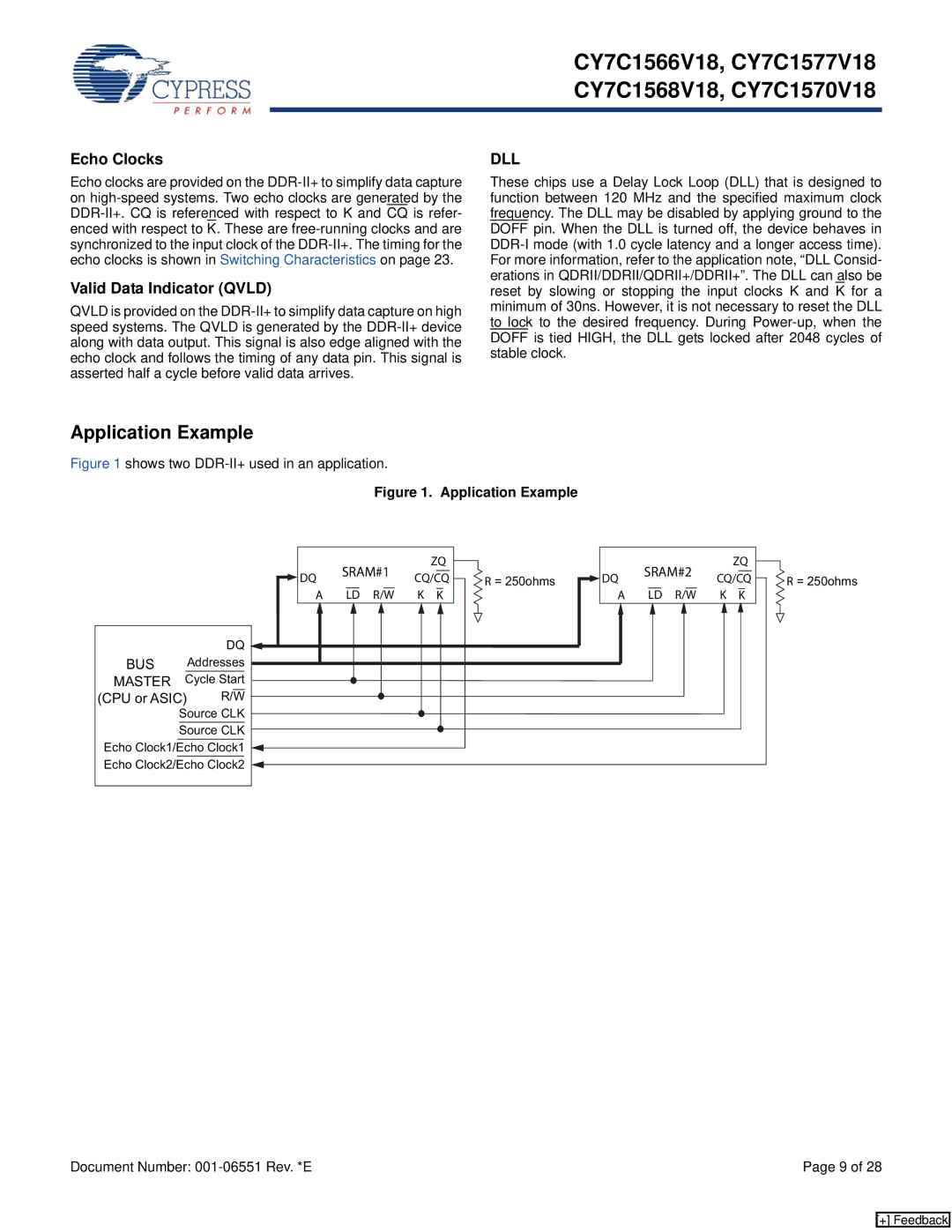

Application Example

Figure 1 shows two DDR-II+ used in an application.

Figure 1. Application Example

|

|

| SRAM#1 |

| ZQ |

|

| SRAM#2 |

| ZQ |

| ||

|

| DQ | CQ/CQ | R = 250ohms | DQ | CQ/CQ | R = 250ohms | ||||||

|

|

|

|

|

| ||||||||

|

| A | LD | R/W | K | K |

| A | LD | R/W | K | K |

|

|

| DQ |

|

|

|

|

|

|

|

|

|

|

|

BUS |

| Addresses |

|

|

|

|

|

|

|

|

|

|

|

MASTER | Cycle Start |

|

|

|

|

|

|

|

|

|

|

| |

(CPU or ASIC) | R/W |

|

|

|

|

|

|

|

|

|

|

| |

| Source CLK |

|

|

|

|

|

|

|

|

|

|

| |

| Source CLK |

|

|

|

|

|

|

|

|

|

|

| |

Echo Clock1/Echo Clock1 |

|

|

|

|

|

|

|

|

|

|

| ||

Echo Clock2/Echo Clock2 |

|

|

|

|

|

|

|

|

|

|

| ||

Document Number: | Page 9 of 28 |

[+] Feedback