CY7C68000A

AC Electrical Characteristics

USB 2.0 Transceiver

USB

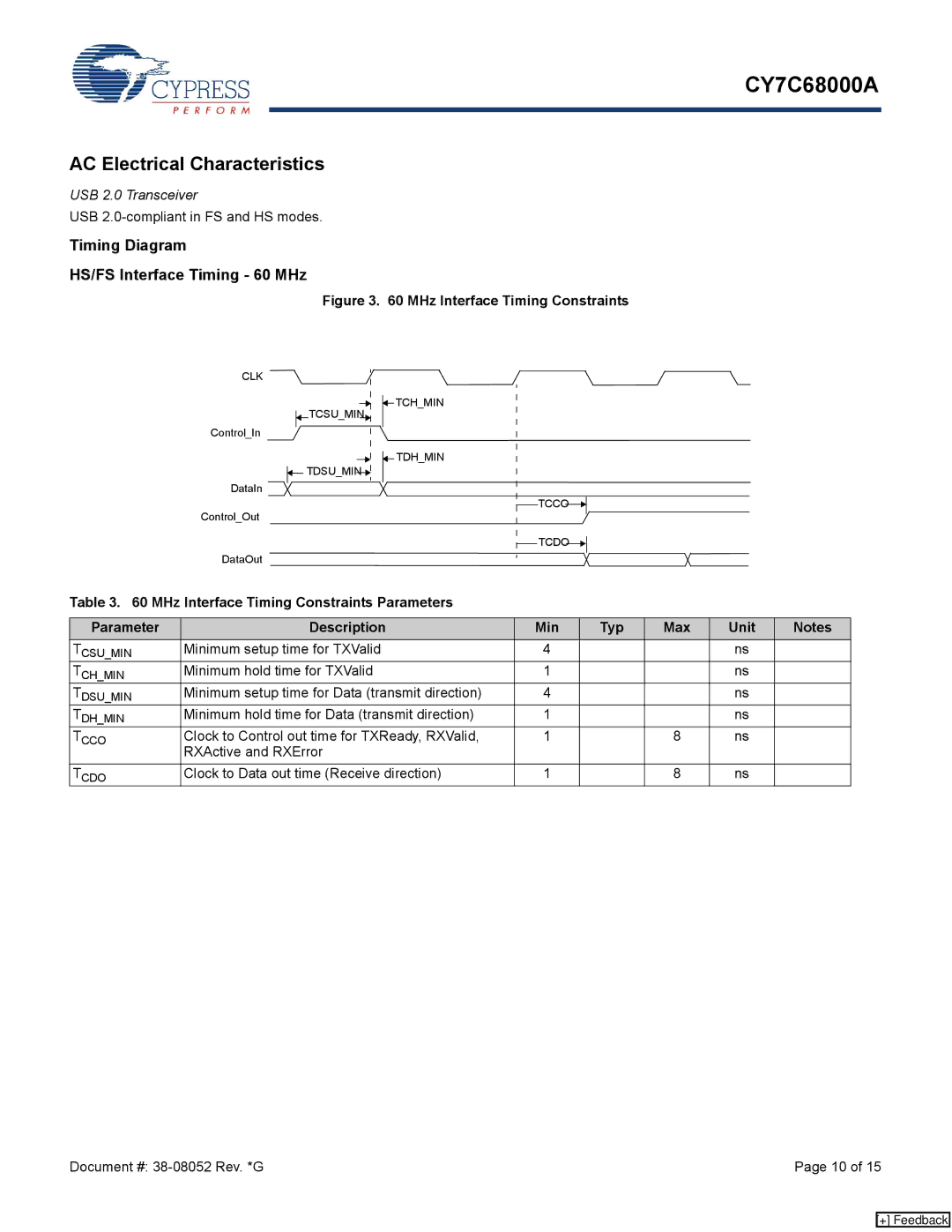

Timing Diagram

HS/FS Interface Timing - 60 MHz

Figure 3. 60 MHz Interface Timing Constraints

CLK

![]() TCH_MIN

TCH_MIN

TCSU_MIN

Control_In

![]() TDH_MIN

TDH_MIN

![]() TDSU_MIN

TDSU_MIN ![]()

![]()

DataIn

TCCO

Control_Out

![]() TCDO

TCDO

DataOut

Table 3. 60 MHz Interface Timing Constraints Parameters

Parameter | Description | Min | Typ | Max | Unit | Notes |

TCSU_MIN | Minimum setup time for TXValid | 4 |

|

| ns |

|

TCH_MIN | Minimum hold time for TXValid | 1 |

|

| ns |

|

TDSU_MIN | Minimum setup time for Data (transmit direction) | 4 |

|

| ns |

|

TDH_MIN | Minimum hold time for Data (transmit direction) | 1 |

|

| ns |

|

TCCO | Clock to Control out time for TXReady, RXValid, | 1 |

| 8 | ns |

|

| RXActive and RXError |

|

|

|

|

|

TCDO | Clock to Data out time (Receive direction) | 1 |

| 8 | ns |

|

Document #: | Page 10 of 15 |

[+] Feedback