STK12C68

Best Practices

nvSRAM products have been used effectively for over 15 years. While

■The nonvolatile cells in an nvSRAM are programmed on the test floor during final test and quality assurance. Incoming inspection routines at customer or contract manufacturer’s sites sometimes reprograms these values. Final NV patterns are typically repeating patterns of AA, 55, 00, FF, A5, or 5A. The end product’s firmware should not assume that an NV array is in a set programmed state. Routines that check memory content values to determine first time system configuration, cold or warm boot status, and so on must always program a unique NV pattern (for example, complex

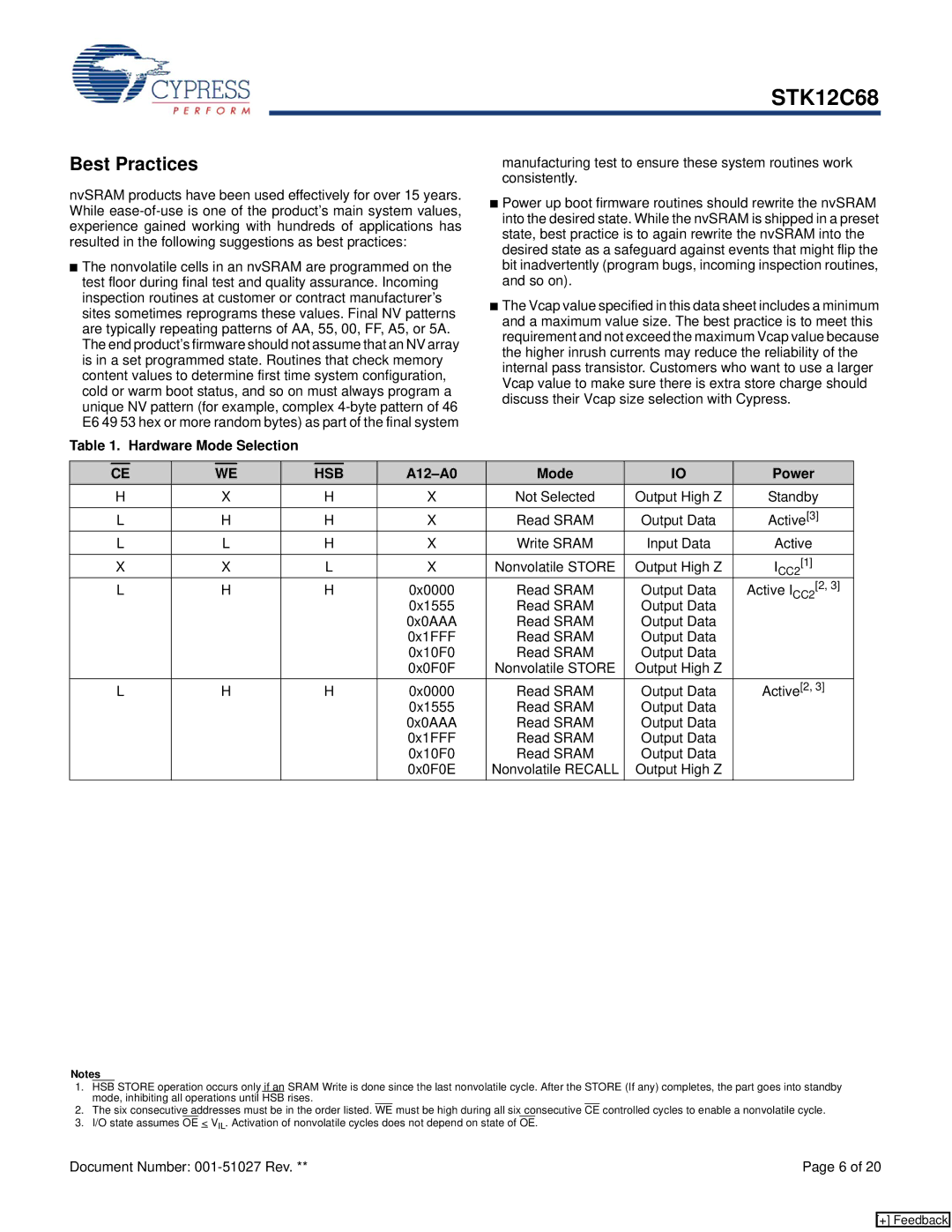

Table 1. Hardware Mode Selection

manufacturing test to ensure these system routines work consistently.

■Power up boot firmware routines should rewrite the nvSRAM into the desired state. While the nvSRAM is shipped in a preset state, best practice is to again rewrite the nvSRAM into the desired state as a safeguard against events that might flip the bit inadvertently (program bugs, incoming inspection routines, and so on).

■The Vcap value specified in this data sheet includes a minimum and a maximum value size. The best practice is to meet this requirement and not exceed the maximum Vcap value because the higher inrush currents may reduce the reliability of the internal pass transistor. Customers who want to use a larger Vcap value to make sure there is extra store charge should discuss their Vcap size selection with Cypress.

CE | WE | HSB |

| Mode | IO | Power |

H | X | H | X | Not Selected | Output High Z | Standby |

L | H | H | X | Read SRAM | Output Data | Active[3] |

L | L | H | X | Write SRAM | Input Data | Active |

X | X | L | X | Nonvolatile STORE | Output High Z | ICC2[1] |

L | H | H | 0x0000 | Read SRAM | Output Data | Active ICC2[2, 3] |

|

|

| 0x1555 | Read SRAM | Output Data |

|

|

|

| 0x0AAA | Read SRAM | Output Data |

|

|

|

| 0x1FFF | Read SRAM | Output Data |

|

|

|

| 0x10F0 | Read SRAM | Output Data |

|

|

|

| 0x0F0F | Nonvolatile STORE | Output High Z |

|

L | H | H | 0x0000 | Read SRAM | Output Data | Active[2, 3] |

|

|

| 0x1555 | Read SRAM | Output Data |

|

|

|

| 0x0AAA | Read SRAM | Output Data |

|

|

|

| 0x1FFF | Read SRAM | Output Data |

|

|

|

| 0x10F0 | Read SRAM | Output Data |

|

|

|

| 0x0F0E | Nonvolatile RECALL | Output High Z |

|

Notes

1.HSB STORE operation occurs only if an SRAM Write is done since the last nonvolatile cycle. After the STORE (If any) completes, the part goes into standby mode, inhibiting all operations until HSB rises.

2.The six consecutive addresses must be in the order listed. WE must be high during all six consecutive CE controlled cycles to enable a nonvolatile cycle.

3.I/O state assumes OE < VIL. Activation of nonvolatile cycles does not depend on state of OE.

Document Number: | Page 6 of 20 |

[+] Feedback