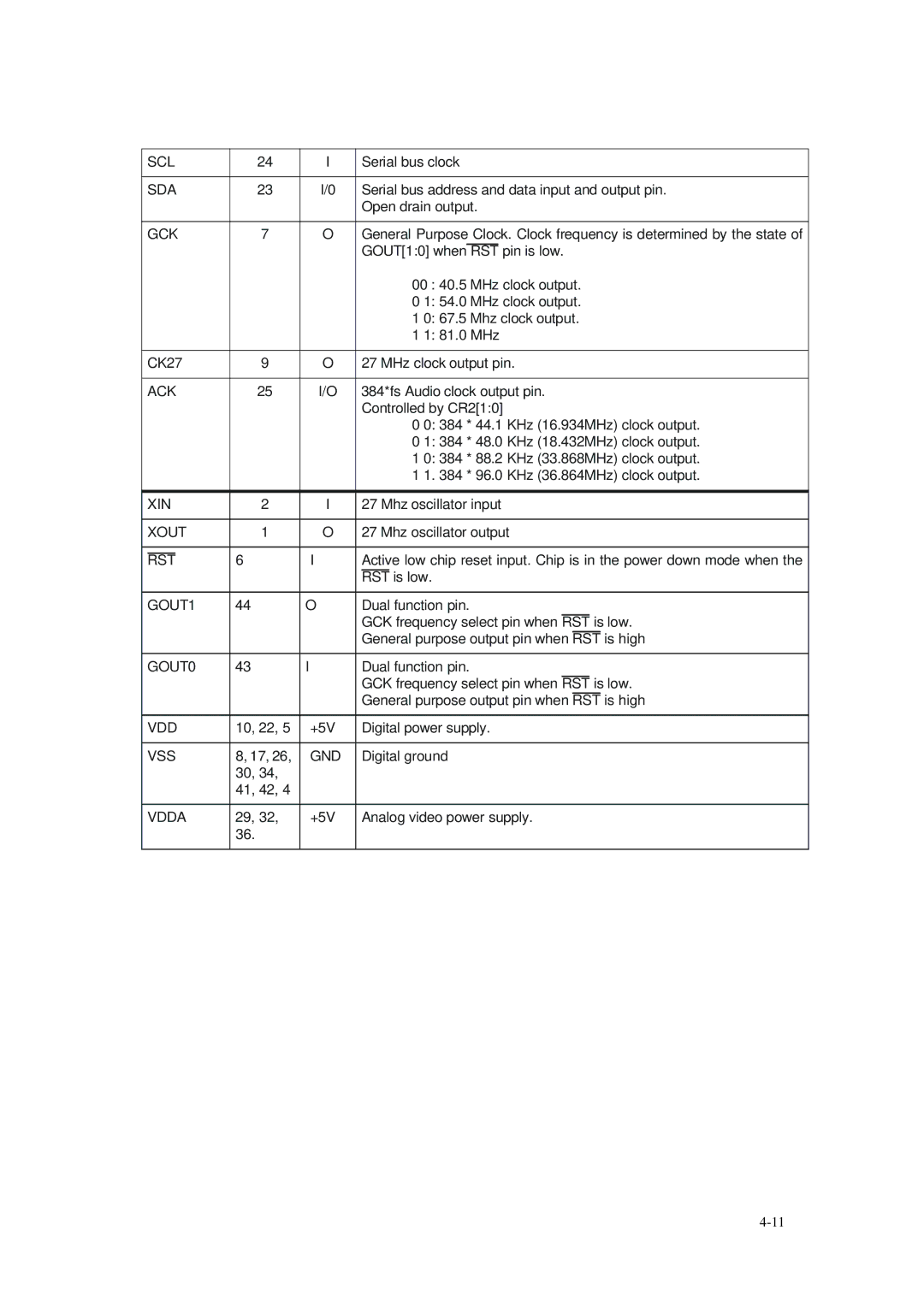

SCL | 24 | I | Serial bus clock | ||||||||

|

|

|

|

|

|

|

|

|

| ||

SDA | 23 | I/0 | Serial bus address and data input and output pin. | ||||||||

|

|

|

|

| Open drain output. | ||||||

|

|

|

|

|

|

|

| ||||

GCK | 7 | O | General Purpose Clock. Clock frequency is determined by the state of | ||||||||

|

|

|

|

| GOUT[1:0] when | RST | pin is low. | ||||

|

|

|

|

| 00 : | 40.5 MHz clock output. | |||||

|

|

|

|

| 0 | 1: | 54.0 MHz clock output. | ||||

|

|

|

|

| 1 | 0: | 67.5 Mhz clock output. | ||||

|

|

|

|

| 1 | 1: | 81.0 MHz | ||||

|

|

|

|

|

|

|

| ||||

CK27 | 9 | O | 27 MHz clock output pin. | ||||||||

|

|

|

|

|

|

|

| ||||

ACK | 25 | I/O | 384*fs Audio clock output pin. | ||||||||

|

|

|

|

| Controlled by CR2[1:0] | ||||||

|

|

|

|

| 0 | 0: | 384 * 44.1 KHz (16.934MHz) clock output. | ||||

|

|

|

|

| 0 | 1: | 384 * 48.0 KHz (18.432MHz) clock output. | ||||

|

|

|

|

| 1 | 0: | 384 * 88.2 KHz (33.868MHz) clock output. | ||||

|

|

|

|

| 1 | 1. | 384 * 96.0 KHz (36.864MHz) clock output. | ||||

|

|

|

|

|

|

|

| ||||

XIN | 2 | I | 27 Mhz oscillator input | ||||||||

|

|

|

|

|

|

|

| ||||

XOUT | 1 | O | 27 Mhz oscillator output | ||||||||

|

|

|

|

|

|

|

| ||||

|

|

| 6 | I | Active low chip reset input. Chip is in the power down mode when the | ||||||

RST | |||||||||||

|

|

|

|

| RST is low. |

|

|

|

|

| |

|

|

|

| ||||||||

GOUT1 | 44 | O | Dual function pin. | ||||||||

|

|

|

|

| GCK frequency select pin when | RST | is low. | ||||

|

|

|

|

| General purpose output pin when RST is high | ||||||

|

|

|

| ||||||||

GOUT0 | 43 | I | Dual function pin. | ||||||||

|

|

|

|

| GCK frequency select pin when | RST | is low. | ||||

|

|

|

|

| General purpose output pin when RST is high | ||||||

|

|

|

| ||||||||

VDD | 10, 22, 5 | +5V | Digital power supply. | ||||||||

|

|

|

| ||||||||

VSS | 8, 17, 26, | GND | Digital ground | ||||||||

|

|

| 30, 34, |

|

|

|

|

|

|

|

|

|

|

| 41, 42, 4 |

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

VDDA | 29, 32, | +5V | Analog video power supply. | ||||||||

|

|

| 36. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|