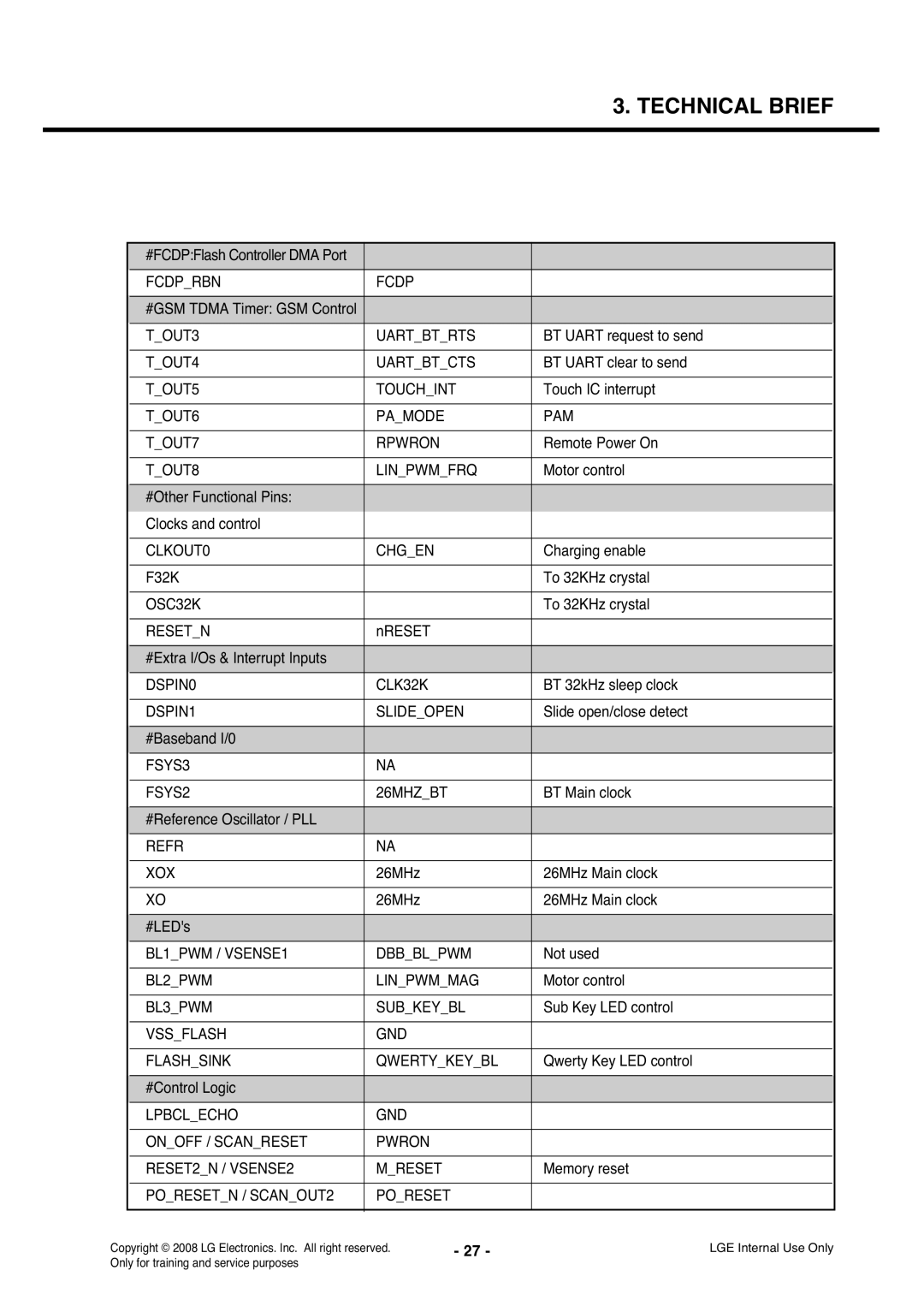

3. TECHNICAL BRIEF

| #FCDP:Flash Controller DMA Port |

|

|

|

|

|

|

|

|

| FCDP_RBN | FCDP |

|

|

|

|

|

|

|

| #GSM TDMA Timer: GSM Control |

|

|

|

|

|

|

| |

| T_OUT3 | UART_BT_RTS | BT UART request to send | |

|

|

|

| |

| T_OUT4 | UART_BT_CTS | BT UART clear to send | |

|

|

|

| |

| T_OUT5 | TOUCH_INT | Touch IC interrupt | |

|

|

|

|

|

| T_OUT6 | PA_MODE |

| PAM |

|

|

|

|

|

| T_OUT7 | RPWRON |

| Remote Power On |

|

|

|

| |

| T_OUT8 | LIN_PWM_FRQ | Motor control | |

|

|

|

|

|

| #Other Functional Pins: |

|

|

|

|

|

|

|

|

| Clocks and control |

|

|

|

|

|

|

|

|

| CLKOUT0 | CHG_EN |

| Charging enable |

|

|

|

|

|

| F32K |

|

| To 32KHz crystal |

|

|

|

|

|

| OSC32K |

|

| To 32KHz crystal |

|

|

|

|

|

| RESET_N | nRESET |

|

|

|

|

|

|

|

| #Extra I/Os & Interrupt Inputs |

|

|

|

|

|

|

|

|

| DSPIN0 | CLK32K |

| BT 32kHz sleep clock |

|

|

|

| |

| DSPIN1 | SLIDE_OPEN | Slide open/close detect | |

|

|

|

|

|

| #Baseband I/0 |

|

|

|

|

|

|

|

|

| FSYS3 | NA |

|

|

|

|

|

|

|

| FSYS2 | 26MHZ_BT |

| BT Main clock |

|

|

|

|

|

| #Reference Oscillator / PLL |

|

|

|

|

|

|

|

|

| REFR | NA |

|

|

|

|

|

|

|

| XOX | 26MHz |

| 26MHz Main clock |

|

|

|

|

|

| XO | 26MHz |

| 26MHz Main clock |

|

|

|

|

|

| #LED's |

|

|

|

|

|

|

| |

| BL1_PWM / VSENSE1 | DBB_BL_PWM | Not used | |

|

|

|

| |

| BL2_PWM | LIN_PWM_MAG | Motor control | |

|

|

|

| |

| BL3_PWM | SUB_KEY_BL | Sub Key LED control | |

|

|

|

|

|

| VSS_FLASH | GND |

|

|

|

|

|

| |

| FLASH_SINK | QWERTY_KEY_BL | Qwerty Key LED control | |

|

|

|

|

|

| #Control Logic |

|

|

|

|

|

|

|

|

| LPBCL_ECHO | GND |

|

|

|

|

|

|

|

| ON_OFF / SCAN_RESET | PWRON |

|

|

|

|

|

|

|

| RESET2_N / VSENSE2 | M_RESET |

| Memory reset |

|

|

|

|

|

| PO_RESET_N / SCAN_OUT2 | PO_RESET |

|

|

|

|

|

|

|

Copyright © 2008 LG Electronics. Inc. All right reserved. | - 27 - | LGE Internal Use Only | ||

Only for training and service purposes |

|

|

| |