AT INTERFACE DESCRIPTION

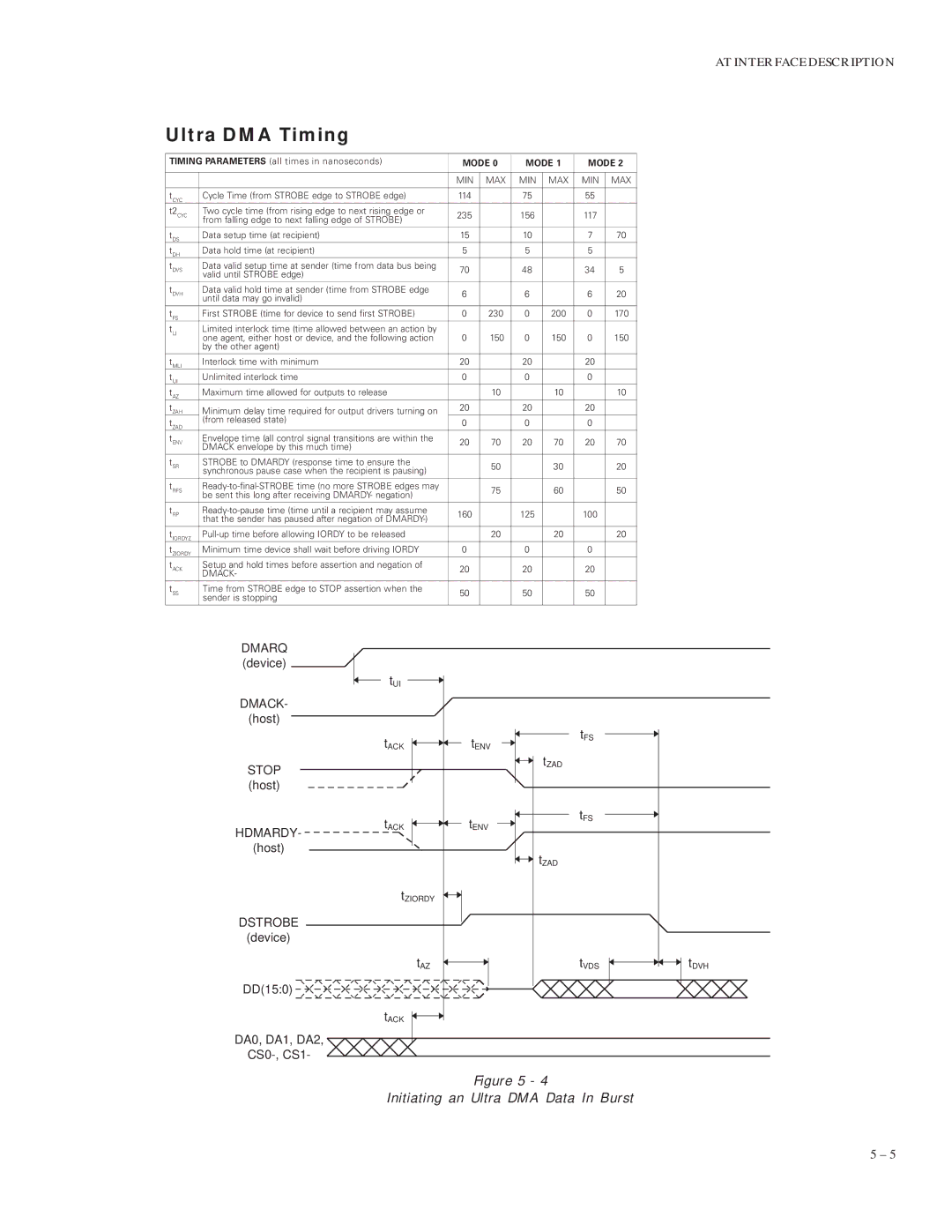

Ultra DMA Timing

TIMING PARAMETERS (all times in nanoseconds) | MODE 0 | MODE 1 | MODE 2 | ||||

|

|

|

|

|

|

|

|

|

| MIN | MAX | MIN | MAX | MIN | MAX |

|

|

|

|

|

|

|

|

tCYC | Cycle Time (from STROBE edge to STROBE edge) | 114 |

| 75 |

| 55 |

|

t2CYC | Two cycle time (from rising edge to next rising edge or | 235 |

| 156 |

| 117 |

|

| from falling edge to next falling edge of STROBE) |

|

|

|

|

|

|

tDS | Data setup time (at recipient) | 15 |

| 10 |

| 7 | 70 |

tDH | Data hold time (at recipient) | 5 |

| 5 |

| 5 |

|

tDVS | Data valid setup time at sender (time from data bus being | 70 |

| 48 |

| 34 | 5 |

| valid until STROBE edge) |

|

|

|

|

|

|

tDVH | Data valid hold time at sender (time from STROBE edge | 6 |

| 6 |

| 6 | 20 |

| until data may go invalid) |

|

|

|

|

|

|

tFS | First STROBE (time for device to send first STROBE) | 0 | 230 | 0 | 200 | 0 | 170 |

tLI | Limited interlock time (time allowed between an action by | 0 | 150 | 0 | 150 | 0 | 150 |

| one agent, either host or device, and the following action | ||||||

| by the other agent) |

|

|

|

|

|

|

tMLI | Interlock time with minimum | 20 |

| 20 |

| 20 |

|

tUI | Unlimited interlock time | 0 |

| 0 |

| 0 |

|

tAZ | Maximum time allowed for outputs to release |

| 10 |

| 10 |

| 10 |

tZAH | Minimum delay time required for output drivers turning on | 20 |

| 20 |

| 20 |

|

tZAD | (from released state) | 0 |

| 0 |

| 0 |

|

|

|

|

| ||||

tENV | Envelope time (all control signal transitions are within the | 20 | 70 | 20 | 70 | 20 | 70 |

| DMACK envelope by this much time) |

|

|

|

|

|

|

tSR | STROBE to DMARDY (response time to ensure the |

| 50 |

| 30 |

| 20 |

| synchronous pause case when the recipient is pausing) |

|

|

|

|

|

|

tRFS |

| 75 |

| 60 |

| 50 | |

| be sent this long after receiving DMARDY- negation) |

|

|

|

|

|

|

tRP | 160 |

| 125 |

| 100 |

| |

| that the sender has paused after negation of |

|

|

|

|

|

|

tIORDYZ |

| 20 |

| 20 |

| 20 | |

tZIORDY | Minimum time device shall wait before driving IORDY | 0 |

| 0 |

| 0 |

|

tACK | Setup and hold times before assertion and negation of | 20 |

| 20 |

| 20 |

|

| DMACK- |

|

|

|

|

|

|

tSS | Time from STROBE edge to STOP assertion when the | 50 |

| 50 |

| 50 |

|

| sender is stopping |

|

|

|

|

|

|

DMARQ |

|

(device) |

|

tUI |

|

DMACK- |

|

(host) |

|

tACK | tENV |

STOP |

|

(host) |

|

tACK | tENV |

HDMARDY- |

|

(host) |

|

tZIORDY |

|

DSTROBE |

|

(device) |

|

tAZ |

|

DD(15:0) |

|

tACK |

|

DA0, DA1, DA2, |

|

|

tFS

tZAD |

|

tFS |

|

tZAD |

|

tVDS | tDVH |

Figure 5 - 4

Initiating an Ultra DMA Data In Burst

5 – 5