Specifications |

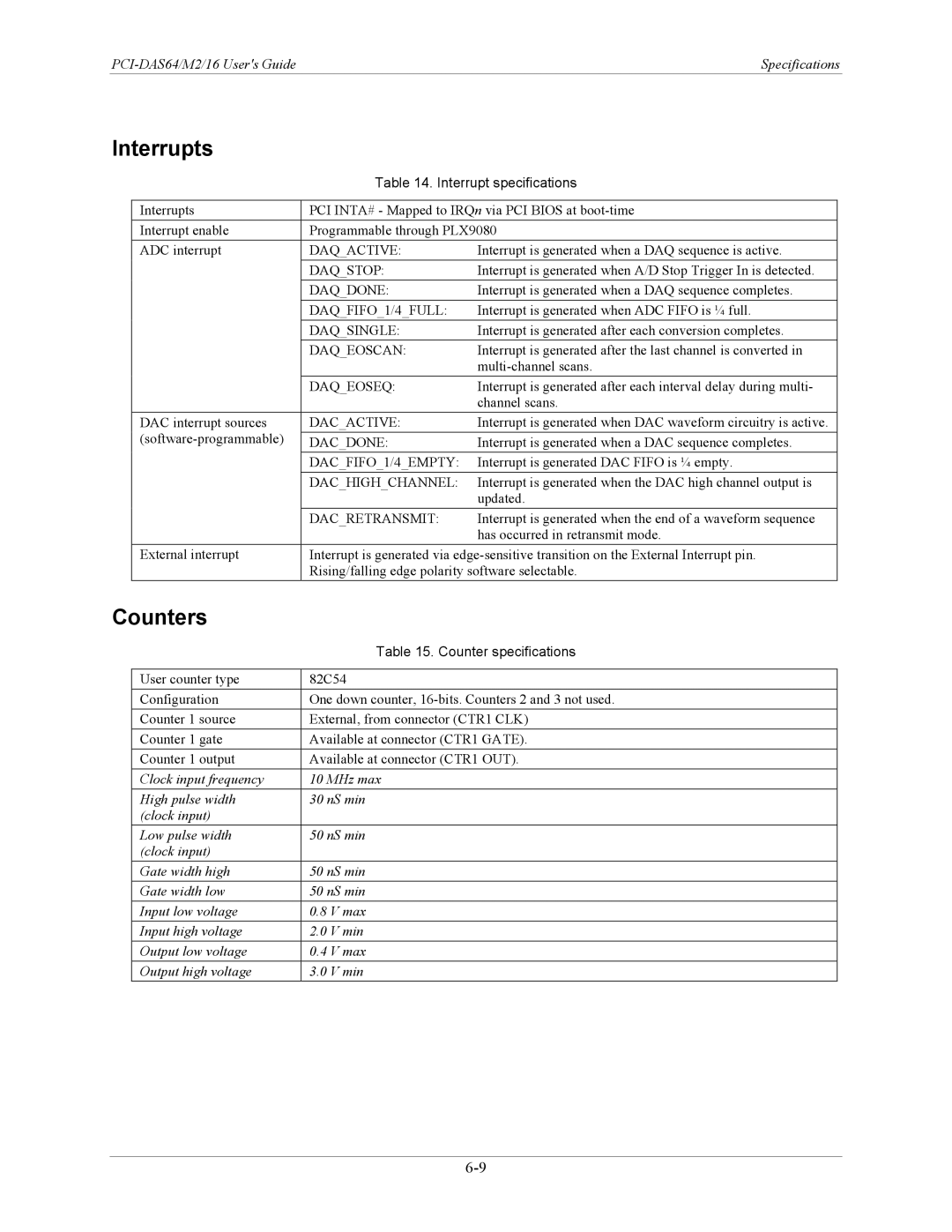

Interrupts

Table 14. Interrupt specifications

Interrupts | PCI INTA# - Mapped to IRQn via PCI BIOS at | |

Interrupt enable | Programmable through PLX9080 | |

ADC interrupt | DAQ_ACTIVE: | Interrupt is generated when a DAQ sequence is active. |

| DAQ_STOP: | Interrupt is generated when A/D Stop Trigger In is detected. |

| DAQ_DONE: | Interrupt is generated when a DAQ sequence completes. |

| DAQ_FIFO_1/4_FULL: | Interrupt is generated when ADC FIFO is ¼ full. |

| DAQ_SINGLE: | Interrupt is generated after each conversion completes. |

| DAQ_EOSCAN: | Interrupt is generated after the last channel is converted in |

|

| |

| DAQ_EOSEQ: | Interrupt is generated after each interval delay during multi- |

|

| channel scans. |

DAC interrupt sources | DAC_ACTIVE: | Interrupt is generated when DAC waveform circuitry is active. |

DAC_DONE: | Interrupt is generated when a DAC sequence completes. | |

| DAC_FIFO_1/4_EMPTY: | Interrupt is generated DAC FIFO is ¼ empty. |

| DAC_HIGH_CHANNEL: | Interrupt is generated when the DAC high channel output is |

|

| updated. |

| DAC_RETRANSMIT: | Interrupt is generated when the end of a waveform sequence |

|

| has occurred in retransmit mode. |

External interrupt | Interrupt is generated via | |

| Rising/falling edge polarity software selectable. | |

Counters

|

| Table 15. Counter specifications |

|

| |

User counter type | 82C54 | |

Configuration | One down counter, | |

Counter 1 source | External, from connector (CTR1 CLK) | |

Counter 1 gate | Available at connector (CTR1 GATE). | |

Counter 1 output | Available at connector (CTR1 OUT). | |

Clock input frequency | 10 MHz max | |

High pulse width | 30 nS min | |

(clock input) |

|

|

Low pulse width | 50 nS min | |

(clock input) |

|

|

Gate width high | 50 nS min | |

Gate width low | 50 nS min | |

Input low voltage | 0.8 | V max |

Input high voltage | 2.0 | V min |

Output low voltage | 0.4 | V max |

Output high voltage | 3.0 | V min |