Freescale Semiconductor, Inc.

ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005

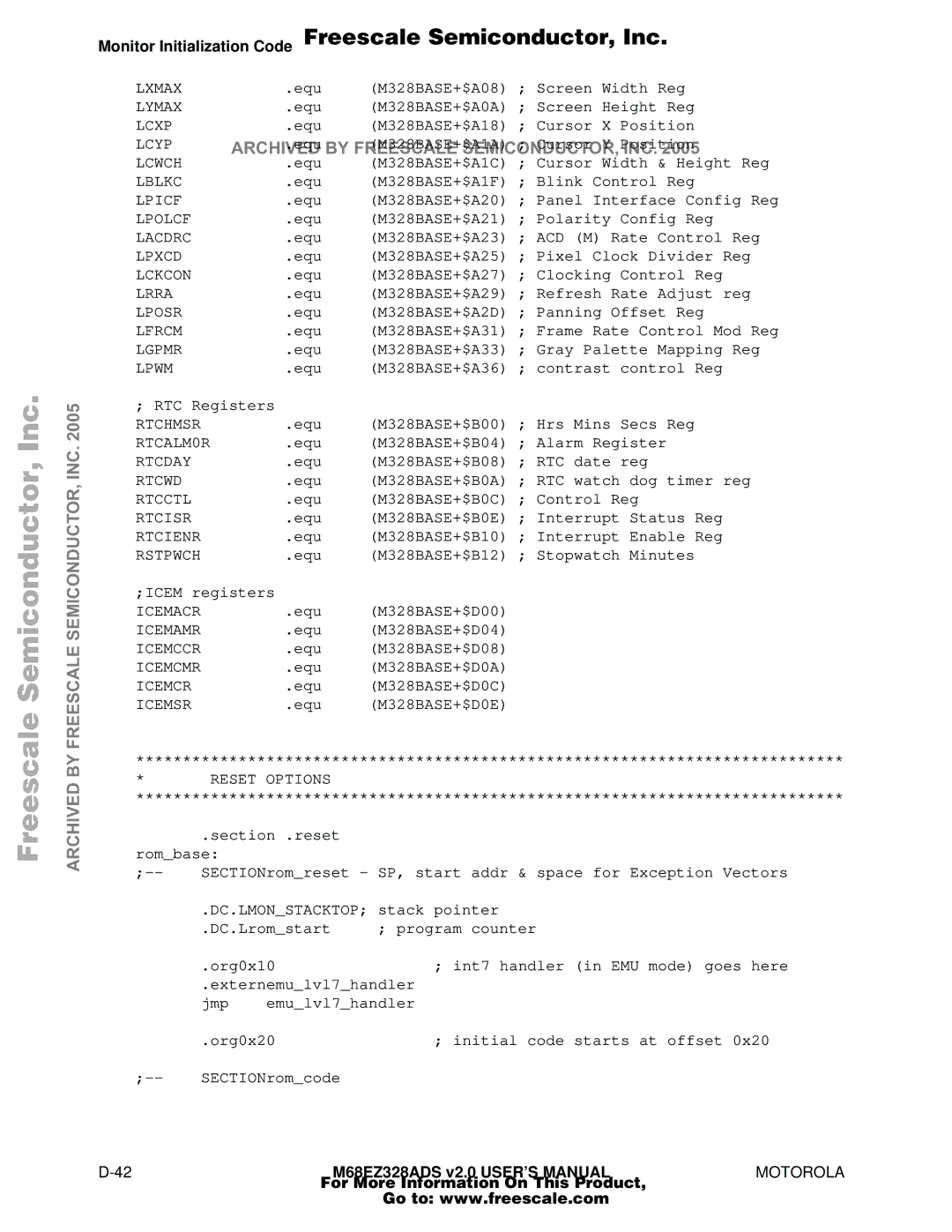

Monitor Initialization Code Freescale Semiconductor, Inc.

LXMAX |

| .equ | (M328BASE+$A08) ; Screen Width Reg | |

LYMAX |

| .equ | (M328BASE+$A0A) ; Screen Height Reg | |

LCXP |

| .equ | (M328BASE+$A18) ; Cursor X Position | |

LCYP | ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005 | |||

| .equ | (M328B | +$A1A) ; Cursor Y Position | |

LCWCH |

| .equ | (M328BASE+$A1C) ; Cursor Width & Height Reg | |

LBLKC |

| .equ | (M328BASE+$A1F) ; Blink Control Reg | |

LPICF |

| .equ | (M328BASE+$A20) ; Panel Interface Config Reg | |

LPOLCF |

| .equ | (M328BASE+$A21) ; Polarity Config Reg | |

LACDRC |

| .equ | (M328BASE+$A23) ; ACD (M) Rate Control Reg | |

LPXCD |

| .equ | (M328BASE+$A25) ; Pixel Clock Divider Reg | |

LCKCON |

| .equ | (M328BASE+$A27) ; Clocking Control Reg | |

LRRA |

| .equ | (M328BASE+$A29) ; Refresh Rate Adjust reg | |

LPOSR |

| .equ | (M328BASE+$A2D) ; Panning Offset Reg | |

LFRCM |

| .equ | (M328BASE+$A31) ; Frame Rate Control Mod Reg | |

LGPMR |

| .equ | (M328BASE+$A33) ; Gray Palette Mapping Reg | |

LPWM |

| .equ | (M328BASE+$A36) ; contrast control Reg | |

; RTC Registers |

|

|

| |

RTCHMSR |

| .equ | (M328BASE+$B00) ; Hrs Mins Secs Reg | |

RTCALM0R |

| .equ | (M328BASE+$B04) ; Alarm Register | |

RTCDAY |

| .equ | (M328BASE+$B08) ; RTC date reg | |

RTCWD |

| .equ | (M328BASE+$B0A) ; RTC watch dog timer reg | |

RTCCTL |

| .equ | (M328BASE+$B0C) ; Control Reg | |

RTCISR |

| .equ | (M328BASE+$B0E) ; Interrupt Status Reg | |

RTCIENR |

| .equ | (M328BASE+$B10) ; Interrupt Enable Reg | |

RSTPWCH |

| .equ | (M328BASE+$B12) ; Stopwatch Minutes | |

;ICEM registers |

|

|

| |

ICEMACR |

| .equ | (M328BASE+$D00) | |

ICEMAMR |

| .equ | (M328BASE+$D04) | |

ICEMCCR |

| .equ | (M328BASE+$D08) | |

ICEMCMR |

| .equ | (M328BASE+$D0A) | |

ICEMCR |

| .equ | (M328BASE+$D0C) | |

ICEMSR |

| .equ | (M328BASE+$D0E) | |

****************************************************************************

*RESET OPTIONS

****************************************************************************

.section .reset rom_base:

| .DC.LMON_STACKTOP; stack pointer | ||

| .DC.Lrom_start | ; program counter | |

| .org0x10 | ; int7 handler (in EMU mode) goes here | |

| .externemu_lvl7_handler | ||

| jmp | emu_lvl7_handler | |

| .org0x20 | ; initial code starts at offset 0x20 | |

SECTIONrom_code |

| ||

For More Information On This Product,

Go to: www.freescale.com