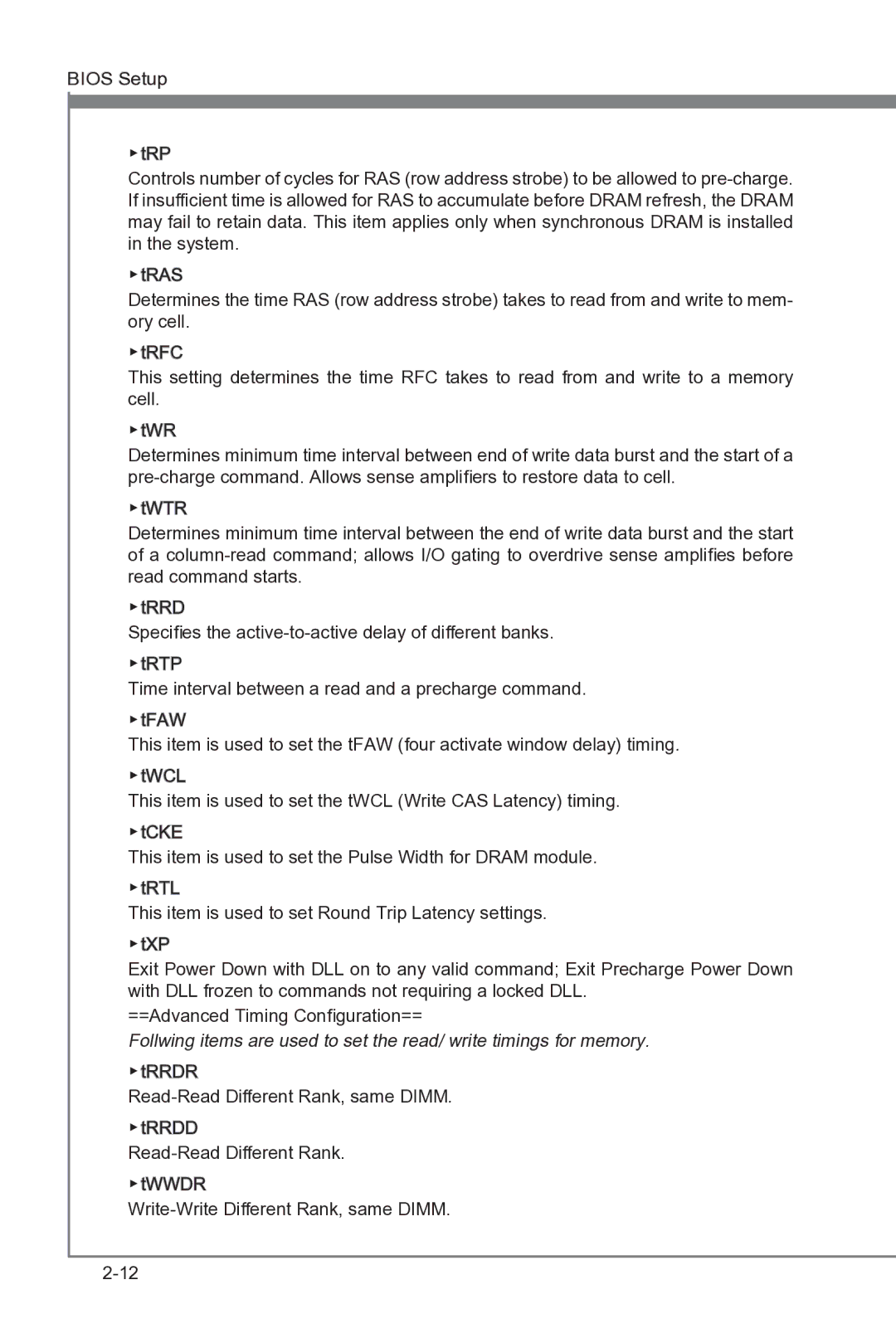

BIOS Setup

▶tRP

Controls number of cycles for RAS (row address strobe) to be allowed to

▶tRAS

Determines the time RAS (row address strobe) takes to read from and write to mem- ory cell.

▶tRFC

This setting determines the time RFC takes to read from and write to a memory cell.

▶tWR

Determines minimum time interval between end of write data burst and the start of a

▶tWTR

Determines minimum time interval between the end of write data burst and the start of a

▶tRRD

Specifies the

Time interval between a read and a precharge command. ▶tFAW

This item is used to set the tFAW (four activate window delay) timing.

▶tWCL

This item is used to set the tWCL (Write CAS Latency) timing.

▶tCKE![]()

This item is used to set the Pulse Width for DRAM module. ▶tRTL

This item is used to set Round Trip Latency settings.

▶tXP

Exit Power Down with DLL on to any valid command; Exit Precharge Power Down with DLL frozen to commands not requiring a locked DLL.

==Advanced Timing Configuration==

Follwing items are used to set the read/ write timings for memory.

▶tRRDR

▶tRRDD

▶tWWDR