¡ Semiconductor |

|

|

|

|

| MSM80C154S/83C154S | ||||||

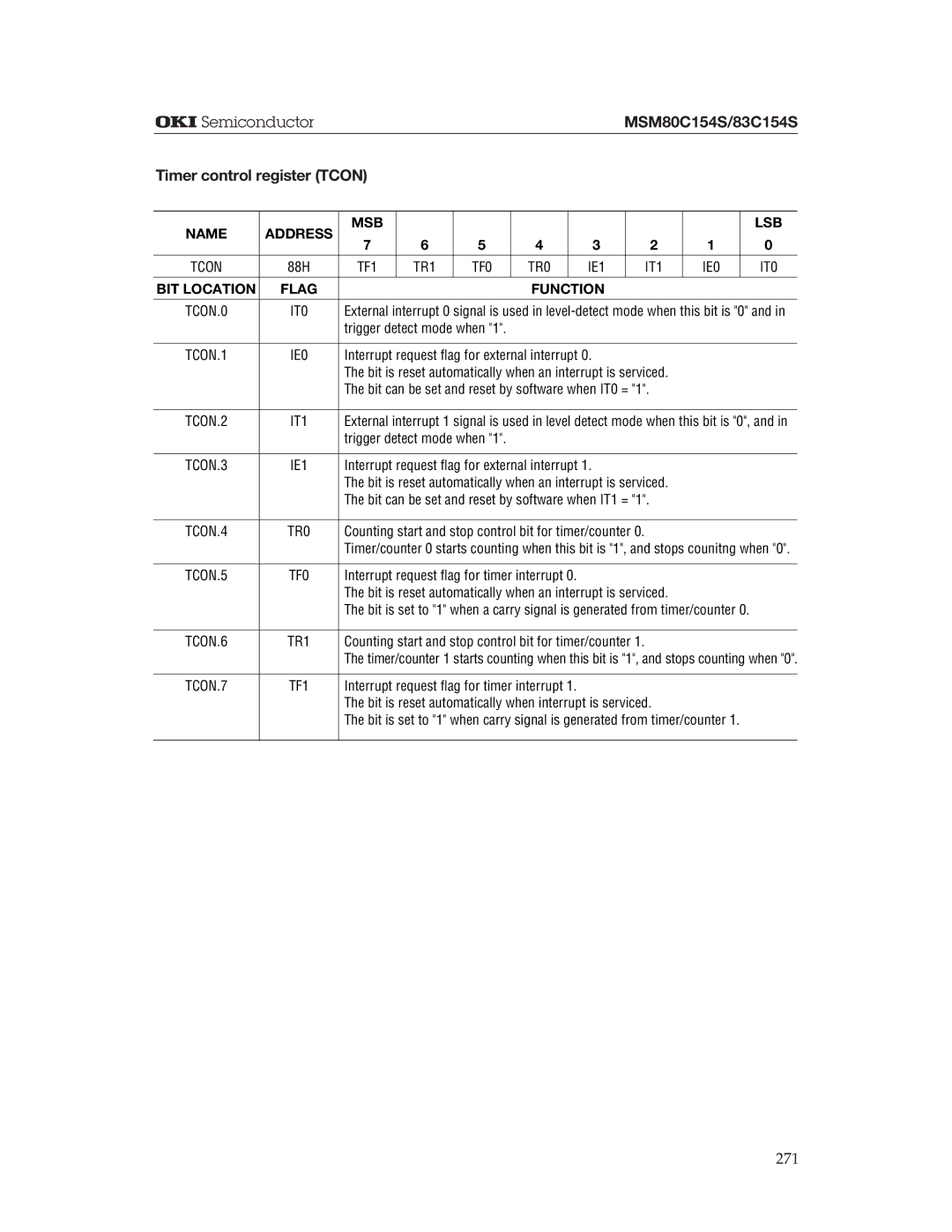

Timer control register (TCON) |

|

|

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

|

|

NAME | ADDRESS | MSB |

|

|

|

|

|

|

|

|

| LSB |

7 | 6 | 5 | 4 |

| 3 |

| 2 | 1 |

| 0 | ||

|

|

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

TCON | 88H | TF1 | TR1 | TF0 | TR0 |

| IE1 |

| IT1 | IE0 |

| IT0 |

|

|

|

|

|

|

|

|

|

|

|

| |

BIT LOCATION | FLAG |

|

|

| FUNCTION |

|

|

|

| |||

|

|

|

|

|

|

|

|

|

| |||

TCON.0 | IT0 | External interrupt 0 signal is used in | ||||||||||

|

| trigger detect mode when "1". |

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

| |

TCON.1 | IE0 | Interrupt request flag for external interrupt 0. |

|

|

|

| ||||||

|

| The bit is reset automatically when an interrupt is serviced. |

|

|

| |||||||

|

| The bit can be set and reset by software when IT0 = "1". |

|

|

| |||||||

|

|

|

|

|

|

|

|

|

| |||

TCON.2 | IT1 | External interrupt 1 signal is used in level detect mode when this bit is "0", and in | ||||||||||

|

| trigger detect mode when "1". |

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

| |

TCON.3 | IE1 | Interrupt request flag for external interrupt 1. |

|

|

|

| ||||||

|

| The bit is reset automatically when an interrupt is serviced. |

|

|

| |||||||

|

| The bit can be set and reset by software when IT1 = "1". |

|

|

| |||||||

|

|

|

|

|

|

|

|

|

|

|

| |

TCON.4 | TR0 | Counting start and stop control bit for timer/counter 0. |

|

|

|

| ||||||

|

| Timer/counter 0 starts counting when this bit is "1", and stops counitng when "0". | ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

TCON.5 | TF0 | Interrupt request flag for timer interrupt 0. |

|

|

|

|

|

| ||||

|

| The bit is reset automatically when an interrupt is serviced. |

|

|

| |||||||

|

| The bit is set to "1" when a carry signal is generated from timer/counter 0. |

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

| |

TCON.6 | TR1 | Counting start and stop control bit for timer/counter 1. |

|

|

|

| ||||||

|

| The timer/counter 1 starts counting when this bit is "1", and stops counting when "0". | ||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

TCON.7 | TF1 | Interrupt request flag for timer interrupt 1. |

|

|

|

|

|

| ||||

|

| The bit is reset automatically when interrupt is serviced. |

|

|

| |||||||

|

| The bit is set to "1" when carry signal is generated from timer/counter 1. |

| |||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

271