MSM80C154S/83C154S |

|

|

|

|

|

| ¡ Semiconductor | |||

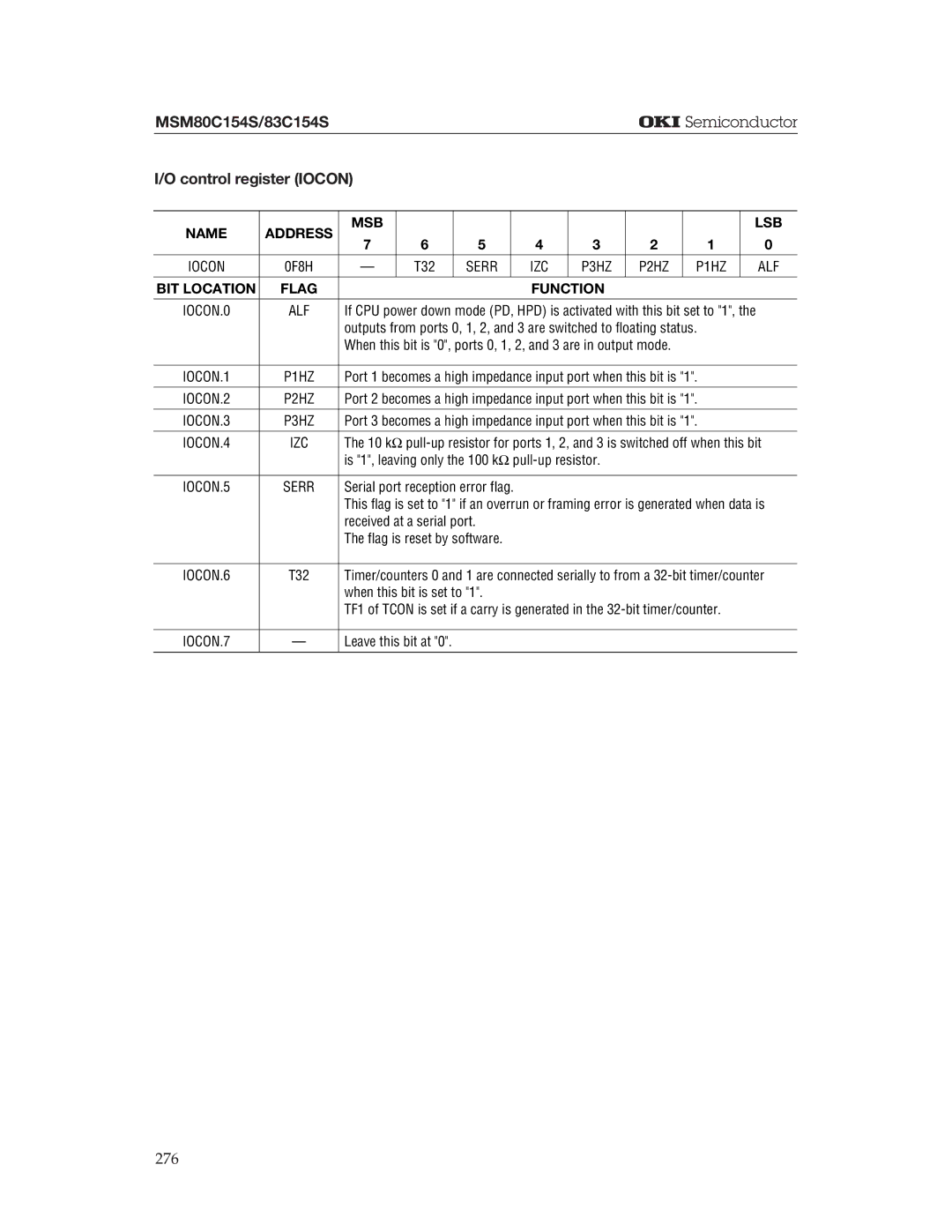

I/O control register (IOCON) |

|

|

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

|

NAME | ADDRESS | MSB |

|

|

|

|

|

|

| LSB |

7 | 6 | 5 |

| 4 | 3 | 2 | 1 | 0 | ||

|

|

| ||||||||

|

|

|

|

|

|

|

|

|

|

|

IOCON | 0F8H | — | T32 | SERR |

| IZC | P3HZ | P2HZ | P1HZ | ALF |

|

|

|

|

|

|

|

|

|

|

|

BIT LOCATION | FLAG |

|

|

|

| FUNCTION |

|

|

| |

|

|

|

|

|

|

|

|

|

| |

IOCON.0 | ALF | If CPU power down mode (PD, HPD) is activated with this bit set to "1", the | ||||||||

|

| outputs from ports 0, 1, 2, and 3 are switched to floating status. |

| |||||||

|

| When this bit is "0", ports 0, 1, 2, and 3 are in output mode. |

|

| ||||||

|

|

|

| |||||||

IOCON.1 | P1HZ | Port 1 becomes a high impedance input port when this bit is "1". |

| |||||||

|

|

|

| |||||||

IOCON.2 | P2HZ | Port 2 becomes a high impedance input port when this bit is "1". |

| |||||||

|

|

|

| |||||||

IOCON.3 | P3HZ | Port 3 becomes a high impedance input port when this bit is "1". |

| |||||||

IOCON.4 | IZC | The 10 kW | ||||||||

|

| is "1", leaving only the 100 kW |

|

|

| |||||

|

|

|

|

|

|

|

| |||

IOCON.5 | SERR | Serial port reception error flag. |

|

|

|

|

| |||

|

| This flag is set to "1" if an overrun or framing error is generated when data is | ||||||||

|

| received at a serial port. |

|

|

|

|

| |||

|

| The flag is reset by software. |

|

|

|

|

| |||

|

|

| ||||||||

IOCON.6 | T32 | Timer/counters 0 and 1 are connected serially to from a | ||||||||

|

| when this bit is set to "1". |

|

|

|

|

| |||

|

| TF1 of TCON is set if a carry is generated in the |

| |||||||

|

|

|

|

|

|

|

|

|

| |

IOCON.7 | — | Leave this bit at "0". |

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

276